Table 119. rx fifo low watermark port 2 ($0x58c), Table 120. rx fifo low watermark port 3 ($0x58d), Rx fifo overflow frame drop counter ports – Intel IXF1104 User Manual

Page 195: 0 - 3 ($0x594 – 0x597), Rx fifo low watermark port 2 ($0x58c), Rx fifo low watermark port 3 ($0x58d)

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

195

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

2

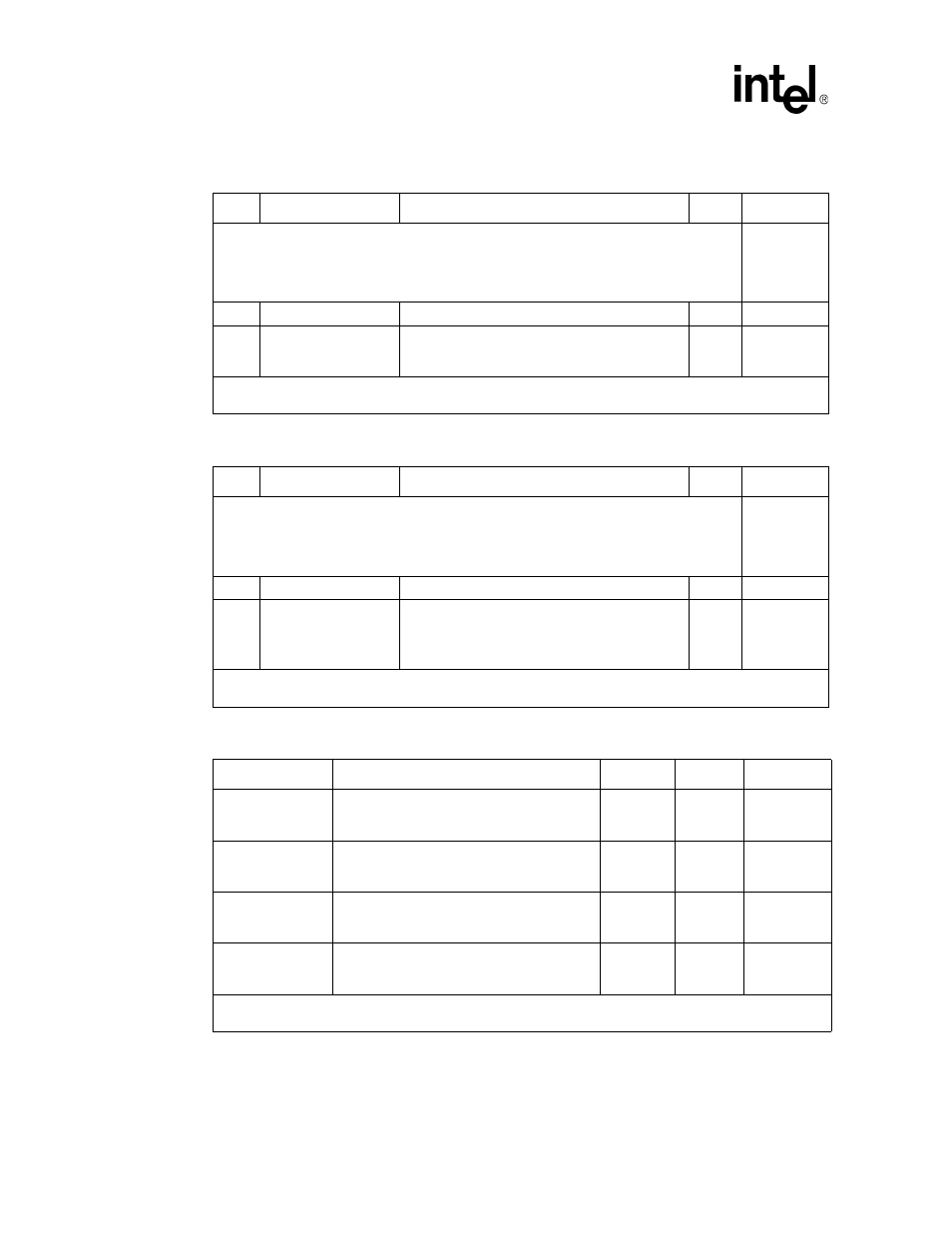

Table 119. RX FIFO Low Watermark Port 2 ($0x58C)

Bit

Name

Description

Type

1

Default

Register Description: The default value of 0x072 represents 114 eight-byte locations. This

equates to 912 bytes of data. A unit entry in this register equates to 8 bytes of data. When the

amount of data stored in the RX FIFO falls below the Low Watermark, flow control is

automatically de-asserted within the MAC to allow more line-side data to be captured by the

RX FIFO.

0x072

31:12

Reserved

Reserved

RO

0x00000

11: 0

RX FIFO Low

Watermark Port 2

The High Watermark value

NOTE: Should never be greater or equal to the

High Watermark.

R/W

0x072

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 120. RX FIFO Low Watermark Port 3 ($0x58D)

Bit

Name

Description

Type

1

Default

Register Description: The default value of 0x072 represents 114 eight-byte locations. This

equates to 912 bytes of data. A unit entry in this register equates to 8 bytes of data. When the

amount of data stored in the RX FIFO falls below the Low watermark, flow control is

automatically de-asserted within the MAC to allow more line-side data to be captured by the

RX FIFO.

0x072

31:12

Reserved

Reserved

RO

0x00000

11: 0

RX FIFO Low

Watermark Port 3

The High watermark value

NOTE: Should never be greater or equal to the

High Watermark.

R/W

0x072

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 121. RX FIFO Overflow Frame Drop Counter Ports 0 - 3 ($0x594 – 0x597)

Name

Description

Address

Type

1

Default

RX FIFO Overflow

Frame Drop

Counter on port 0

When RX FIFO on port 0 becomes full or

reset, the number of frames lost/dropped on

this port are shown in this register.

0x594

R

0x00000000

RX FIFO Overflow

Frame Drop

Counter on port 1

When RX FIFO on port 1 becomes full or

reset, the number of frames lost/dropped on

this port are shown in this register.

0x595

R

0x00000000

RX FIFO Overflow

Frame Drop

Counter on port 2

When RX FIFO on port 2 becomes full or

reset, the number of frames lost/dropped on

this port are shown in this register.

0x596

R

0x00000000

RX FIFO Overflow

Frame Drop

Counter on port 3

When RX FIFO on port 3 becomes full or

reset, the number of frames lost/dropped on

this port are shown in this register.

0x597

R

0x00000000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No clear;

R/W/C = Read/Write, Clear on Write