Figure 23. serdes receiver jitter tolerance, 6 transmit jitter, 7 receive jitter – Intel IXF1104 User Manual

Page 106: Transmit jitter, Receive jitter, Serdes receiver jitter tolerance

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

106

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

5.6.2.6

Transmit Jitter

The SerDes core total transmit jitter, including contributions from the intermediate frequency PLL,

is comprised of the following two components:

•

A deterministic component attributed to the SerDes core’s architectural characteristics

•

A random component attributed to random thermal noise effects

Since the thermal noise component is random and statistical in nature, the SerDes core total

transmit jitter must be specified as a function of BER.

5.6.2.7

Receive Jitter

The SerDes core total receiver jitter, including contributions from the intermediate frequency PLL,

is comprised of the following two components:

•

A deterministic component attributed to the SerDes core architectural characteristics

•

A random component attributed to random thermal noise effects.

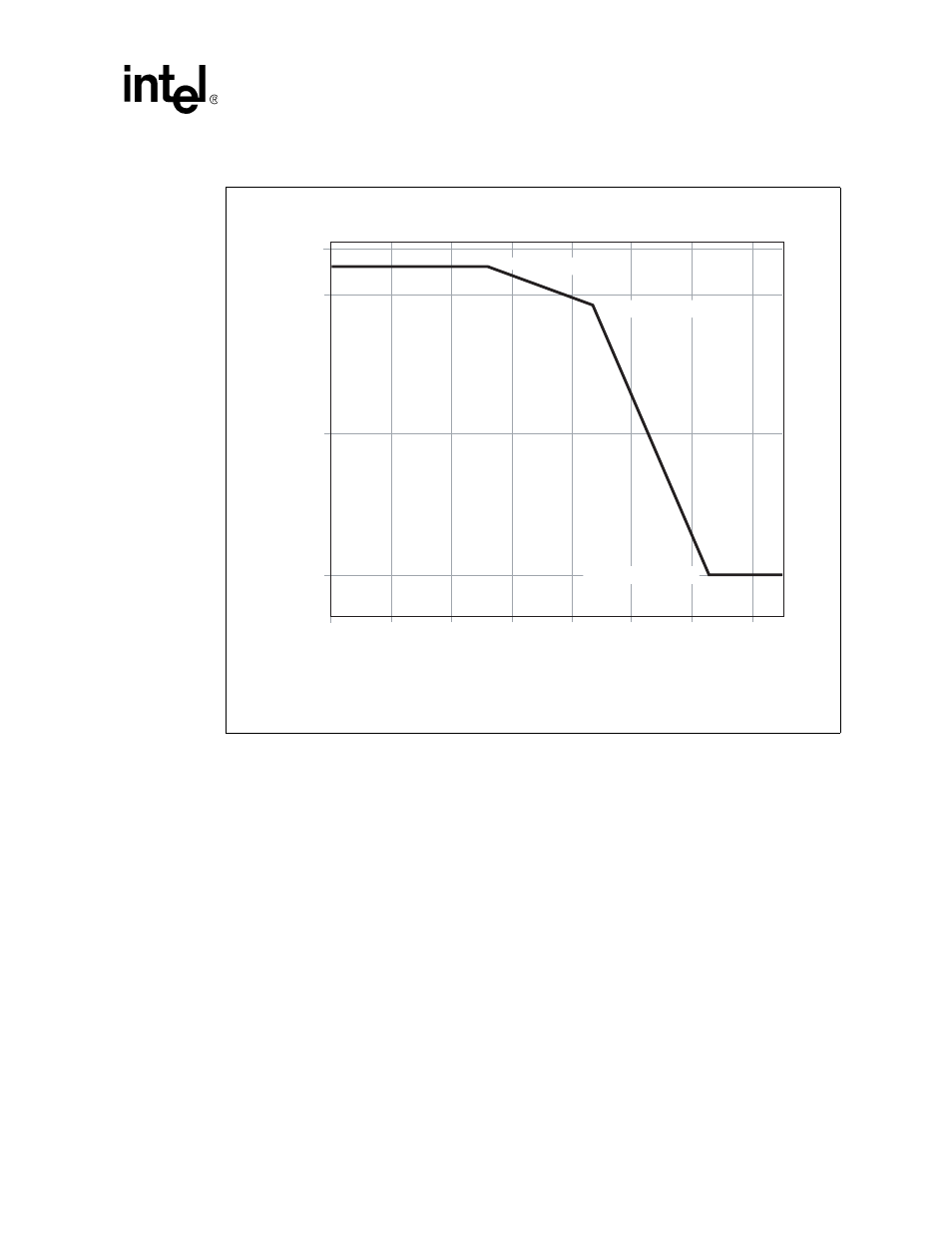

Figure 23. SerDes Receiver Jitter Tolerance

Note:

UI = Unit interval.

B0745-02

10-1

0

10+1

10

0

10

1

10

2

10

3

10

4

10

5

10

6

10

7

Frequency

Sinusoidal Jitter Mask

Peak-to-Peak Amplitude (UI)

16 ui

375 Hz 16 ui

22.5836 kHz 8.5 ui

1.9195 MHz 0.1 ui