Tx fifo port reset ($0x620), For the – Intel IXF1104 User Manual

Page 207

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

207

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

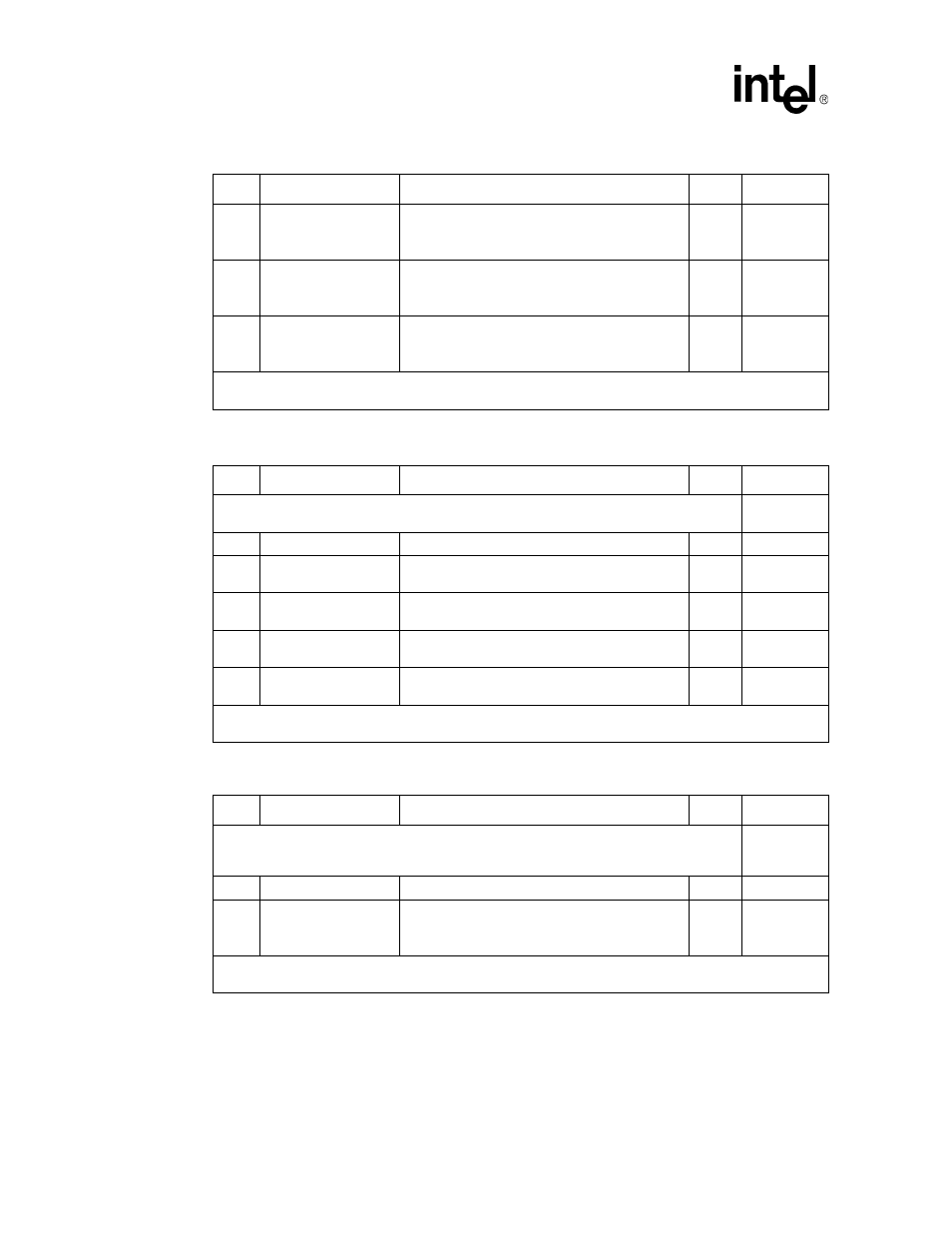

2

FOE2

Port 2

0 = FIFO overflow event did not occur

1 = FIFO overflow event occurred

R

0

1

FOE1

Port 1

0 = FIFO overflow event did not occur

1 = FIFO overflow event occurred

R

0

0

FOE0

Port 0

0 = FIFO overflow event did not occur

1 = FIFO overflow event occurred

R

0

Table 136. Loop RX Data to TX FIFO (Line-Side Loopback) Ports 0 - 3 ($0x61F)

Bit

Name

Description

Type

1

Default

Register Description: This register enables data received from the line-side receive interface

through the MAC to be sent to the TX FIFO and back to the line-side transmit interface.

0x00000000

31:4

Reserved

Reserved

RO

0x0000000

3

Port 3 Line-Side

Loopback

0 = Disable line-side loopback

1 = Enable line-side loopback

R/W

0

2

Port 2 Line-Side

Loopback

0 = Disable line-side loopback

1 = Enable line-side loopback

R/W

0

1

Port 1 Line-Side

Loopback

0 = Disable line-side loopback

1 = Enable line-side loopback

R/W

0

0

Port 0 Line-Side

Loopback

0 = Disable line-side loopback

1 = Enable line-side loopback

R/W

0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 137. TX FIFO Port Reset ($0x620) (Sheet 1 of 2)

Bit

Name

Description

Type

1

Default

Register Description: This is a port reset register for each port in the TX block. Port ID = bit

position in the register. To make the port active, the bit must be set to Low. (For example, reset

of Port 3 implies register value = 1000, setting the bit to 1 asserts the port reset).

0x00000000

31:4

Reserved

Reserved

RO

0x0000000

3

Port 3 Reset

Port 3

0 = De-assert Reset

1 = Assert Reset

R/W

0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 135. TX FIFO Overflow/Underflow/Out of Sequence Event ($0x61E) (Sheet 2 of 2)

Bit

Name

Description

Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write