Intel IXF1104 User Manual

Page 216

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

216

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

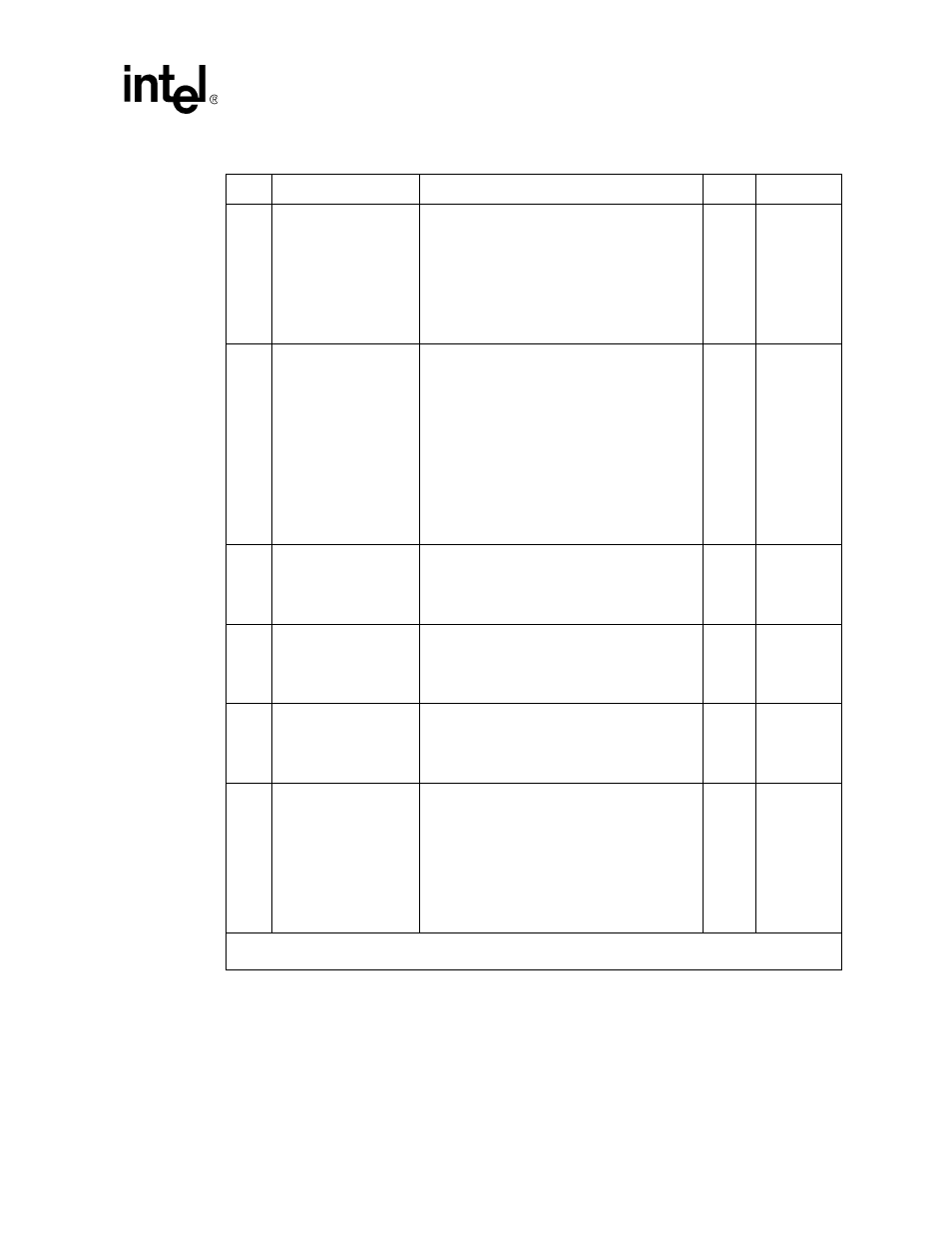

25

B2B_PAUSE Port 1

SPHY Mode:

Indicates the number of pause cycles to be

introduced between back-to-back transfers for

port 1.

0 = Zero pause cycles

1 = Two pause cycles

MPHY Mode:

NA

R/W

0

24

B2B_PAUSE Port 0

SPHY Mode:

Indicates the number of pause cycles to be

introduced between back-to-back transfers for

port 0.

0 = Zero pause cycles

1 = Two pause cycles

MPHY Mode:

Indicates the number of pause cycles to be

introduced between back-to-back transfers for all

ports.

0 = Zero pause cycles

1 = Two pause cycles

R/W

0

23:22

RX_BURST Port 3

SPHY Mode:

NA

MPHY Mode:

NA

R/W

0x0

21:20

RX_BURST Port 2

SPHY Mode:

NA

MPHY Mode:

NA

R/W

0x0

19:18

RX_BURST Port 1

SPHY Mode:

NA

MPHY Mode:

NA

R/W

0x0

17:16

RX_BURST Port 0

SPHY Mode:

NA

MPHY Mode:

Selects the maximum burst size on the RX path

for all ports.

0x = 64 bytes maximum burst size

10 = 128 bytes maximum burst size

11 = 256 bytes maximum burst size

R/W

0x0

Table 147. SPI3 Receive Configuration ($0x701) (Continued) (Sheet 2 of 4)

Bit

Name

Description

Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write