Intel IXF1104 User Manual

Page 218

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

218

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

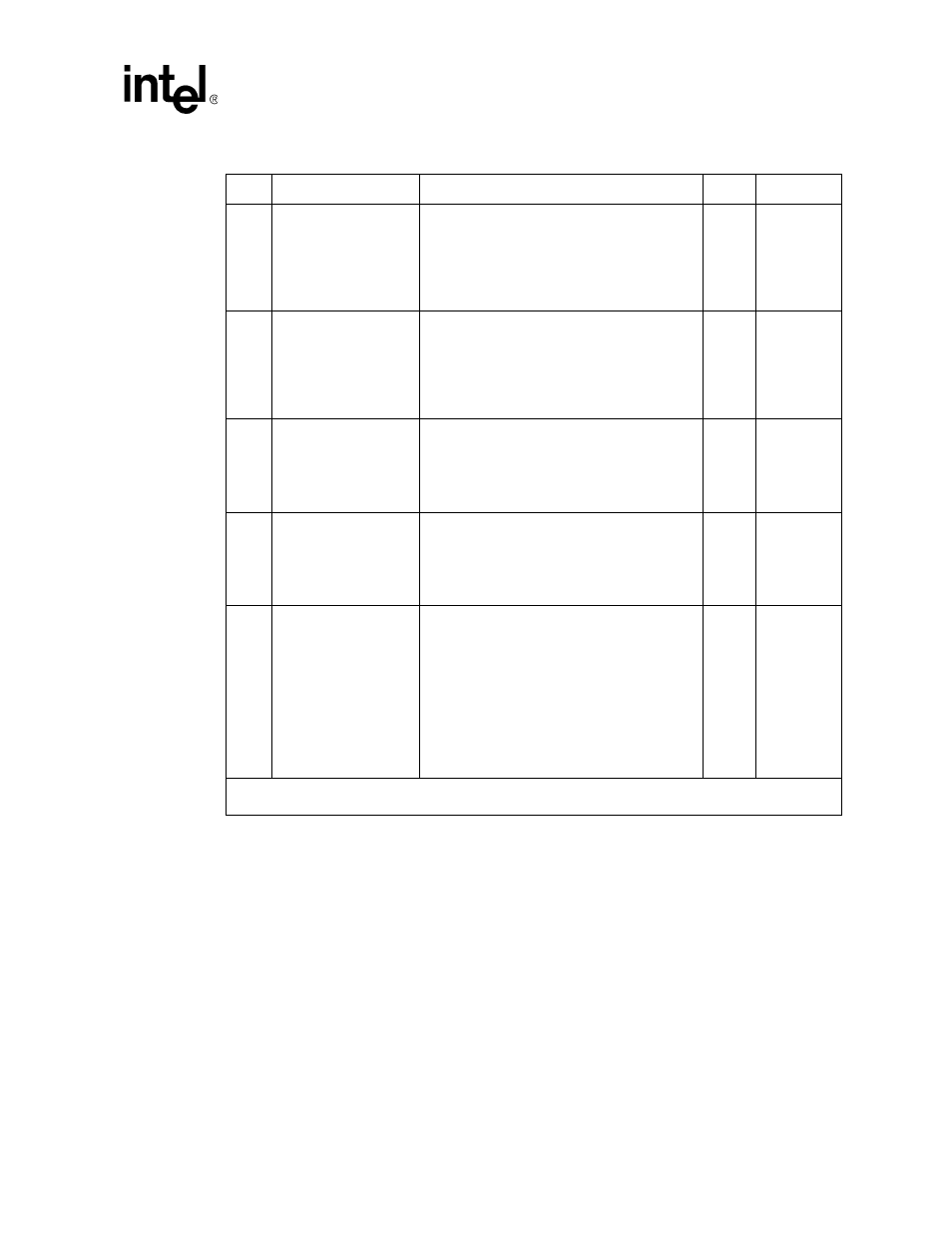

9

Rx_port_enable

Port 1

SPHY Mode:

0 = Disables the selected SPI3 RX port.

1 = Enables the selected SPI3 RX port.

MPHY Mode:

0 = Disables the selected SPI3 RX port.

1 = Enables the selected SPI3 RX port.

R/W

0x1

8

Rx_port_enable

Port 0

SPHY Mode:

0 = Disables the selected SPI3 RX port.

1 = Enables the selected SPI3 RX port.

MPHY Mode:

0 = Disables the selected SPI3 RX port.

1 = Enables the selected SPI3 RX port.

R/W

0x1

7

Rx_core_enable

SPHY Mode:

NA. Write as 1, ignore on Read.

MPHY Mode:

0 = Disables the RX SPI3 core.

1 = Enables the RX SPI3 core.

R/W

0x1

6:1

IBA[5:0]

SPHY Mode:

NA. Write as 0, ignore on Read.

MPHY Mode:

Sets the 6-bit value appended to the 2-bit

address during the port address selection.

R/W

0x00

0

RERR_enable

SPHY Mode/MPHY Mode:

Frames marked to be filtered (based on the

settings in the

Frame Size (Addr: Port_Index + 0x0F)”

that are

not dropped in the RX FIFO (see

Errored Frame Drop Enable ($0x59F)”

can be

optionally indicated with an RERR when sent out

the SPI3 interface.

0 = Packets not indicated with RERR.

1 = Packets indicated with RERR.

R/W

0

Table 147. SPI3 Receive Configuration ($0x701) (Continued) (Sheet 4 of 4)

Bit

Name

Description

Type

1

Default

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write