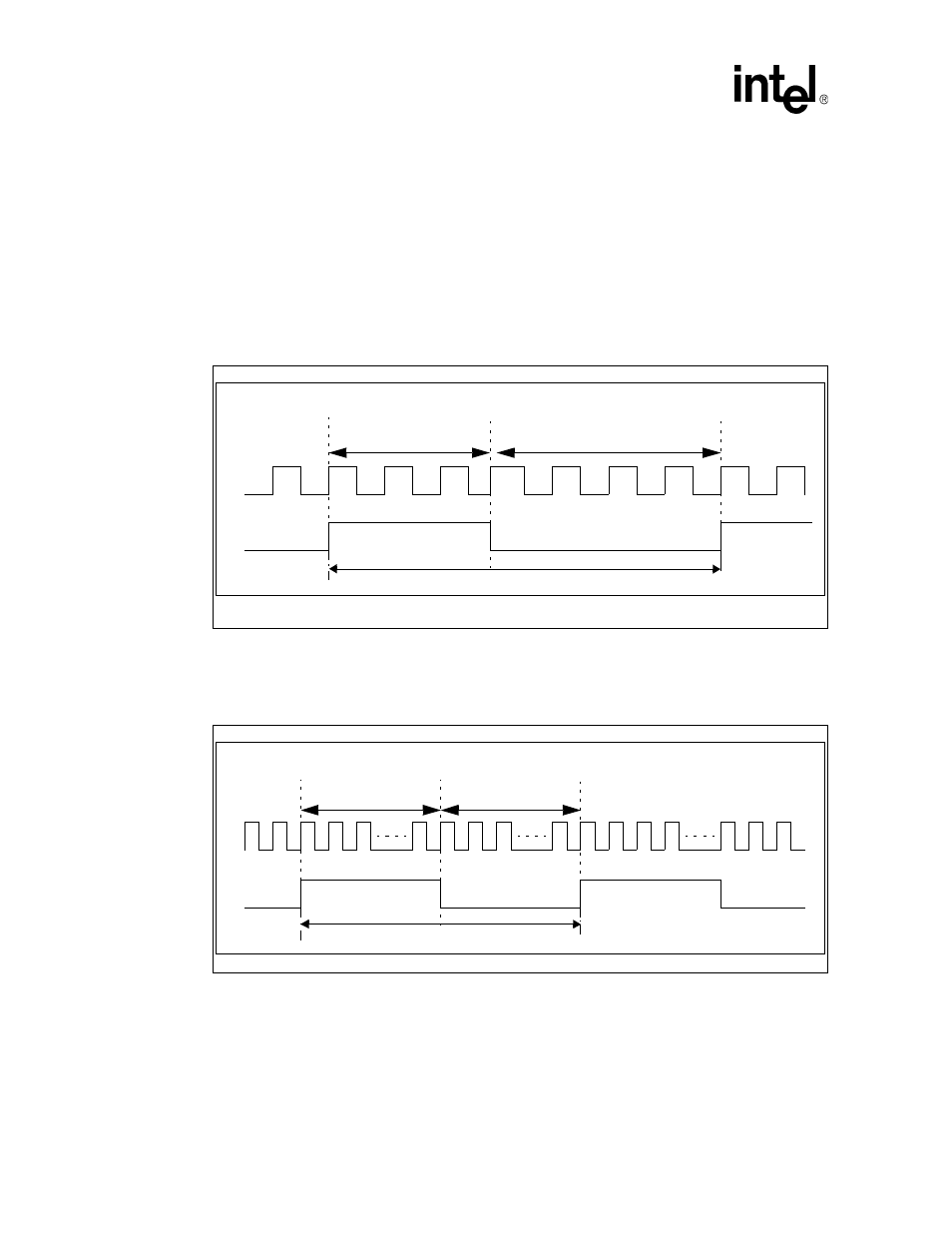

6 mdio ac timing specification, 1 mdc high-speed operation timing, Figure 41. mdc high-speed operation timing – Intel IXF1104 User Manual

Page 145: 2 mdc low-speed operation timing, Figure 42. mdc low-speed operation timing, Mdio ac timing specification 7.6.1, Mdc high-speed operation timing, Mdc low-speed operation timing

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

145

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

7.6

MDIO AC Timing Specification

The MDIO Interface on the IXF1104 MAC can operate in two modes – low-speed and high-speed.

In low-speed mode, the MDC clock signal operates at a frequency of 2.5 MHz. In high-speed

mode, the MDC clock signal operates at a frequency of 18 MHz. (See

through

and

7.6.1

MDC High-Speed Operation Timing

7.6.2

MDC Low-Speed Operation Timing

Figure 41. MDC High-Speed Operation Timing

Figure 42. MDC Low-Speed Operation Timing

24 ns

(3 X 125 MHz clocks)

32 ns

(4 X 125 MHz clocks)

MDC

56 ns (17.85 MHz)

200 ns

(25 X 125 MHz clocks)

200 ns

(25 X 125 MHz clocks)

MDC

400 ns (2.5 MHz)