10 serdes register overview, Table 150. tx and rx power-down ($0x787), Tx driver power level ports 0 - 3 ($0x784) – Intel IXF1104 User Manual

Page 220: Tx and rx power-down ($0x787), Rx signal detect level ports 0 - 3 ($0x793), Register, F pa

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

Datasheet

220

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

8.4.10

SerDes Register Overview

through

Table 152 “Clock and Interface Mode Change Enable Ports 0 - 3 ($0x794)” on

define the contents of the SerDes registers at base location 0x780, which contain the

control and status for the four SerDes interfaces on the IXF1104 MAC.

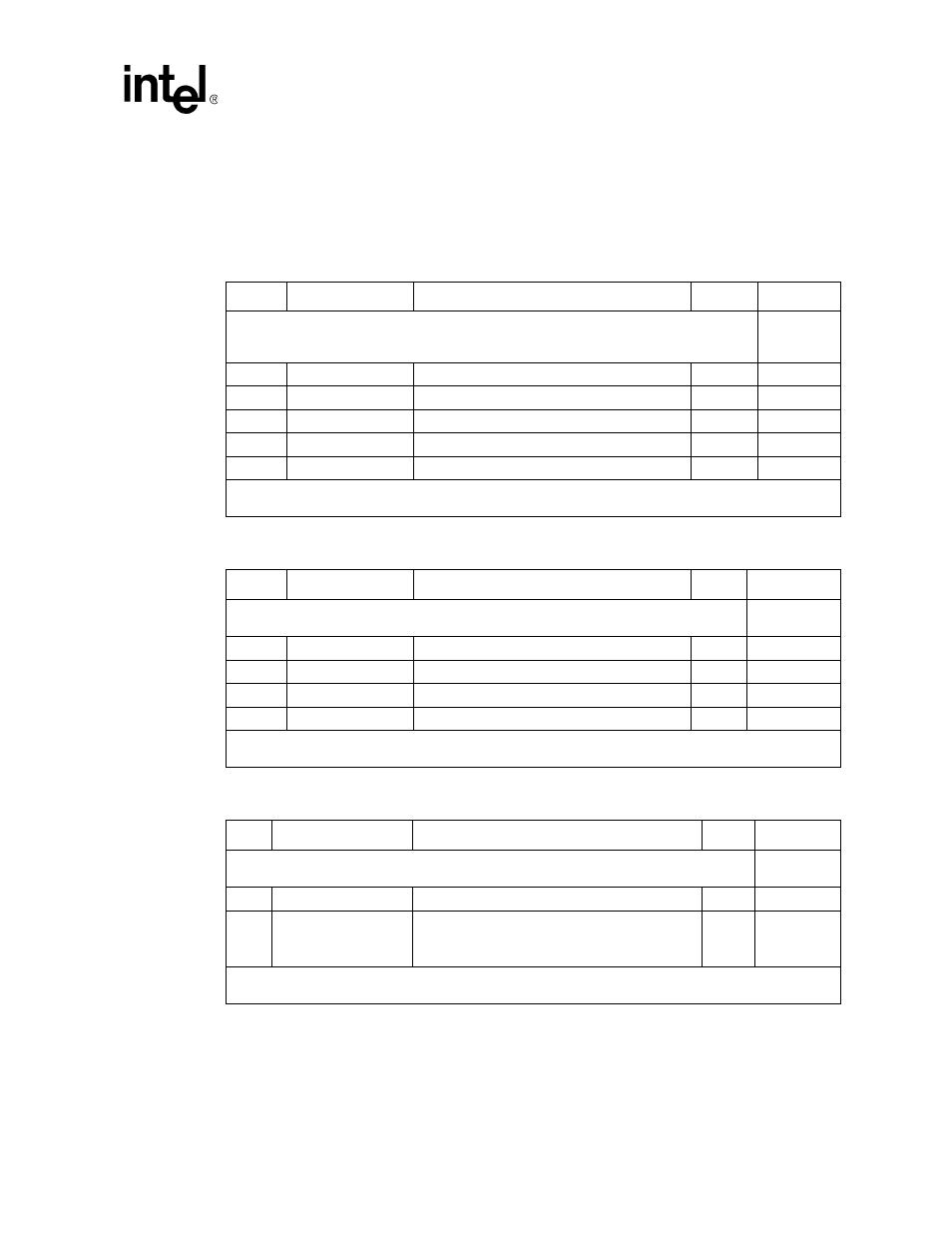

Table 149. TX Driver Power Level Ports 0 - 3 ($0x784)

Bit

Name

Description

Type

Default

Register Description: Allows selection of various programmable drive strengths on each

SerDes port. Refer to

Section 5.6.2.2, “Transmitter Programmable Driver-Power Levels” on

.

0x0000dddd

31:16

Reserved

Reserved

RO

0x0000

15:12

DRVPWR3[3:0]

Encoded input that sets Power Level for Port 3

R/W

1101

11:8

DRVPWR2[3:0]

Encoded input that sets Power Level for Port 2

R/W

1101

7:4

DRVPWR1[3:0]

Encoded input that sets Power Level for Port 1

R/W

1101

3:0

DRVPWR0[3:0]

Encoded input that sets Power Level for Port 0

R/W

1101

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 150. TX and RX Power-Down ($0x787)

Bit

Name

Description

Type

Default

Register Description: TX and RX power-down bits to allow per-port power-down of unused

ports

0x00000000

31:14 Reserved

Reserved

RO

0x0000000

13:10

TPWRDWN[3:0]

TX power-down for Ports 3-0 (1 = Power-down)

R/W

0000

9:4

Reserved

Reserved

RO

0x00

3:0

RPWRDWN[3:0]

RX Power-down for Ports 3-0 (1 = Power-down)

R/W

0000

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 151. RX Signal Detect Level Ports 0 - 3 ($0x793)

Bit

Name

Description

Type

1

Default

Register Description: This register shows the status of the Rx input in relation to the level of

the signal being received from the line. This register is meant for debug and test use.

0x00000000

31:4

Reserved

Reserved

RO

0x0000000

3:0

SIGDET[3:0]

Signal Detect for Ports 0-3

0 = Noise

1 = Signal

RO

0x0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write