Table 83. flush tx ($ port_index + 0x11), Mac if mode and rgmii speed ($ port_index + 0x10), Flush tx ($ port_index + 0x11) – Intel IXF1104 User Manual

Page 167

Intel

®

IXF1104 4-Port Gigabit Ethernet Media Access Controller

167

Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

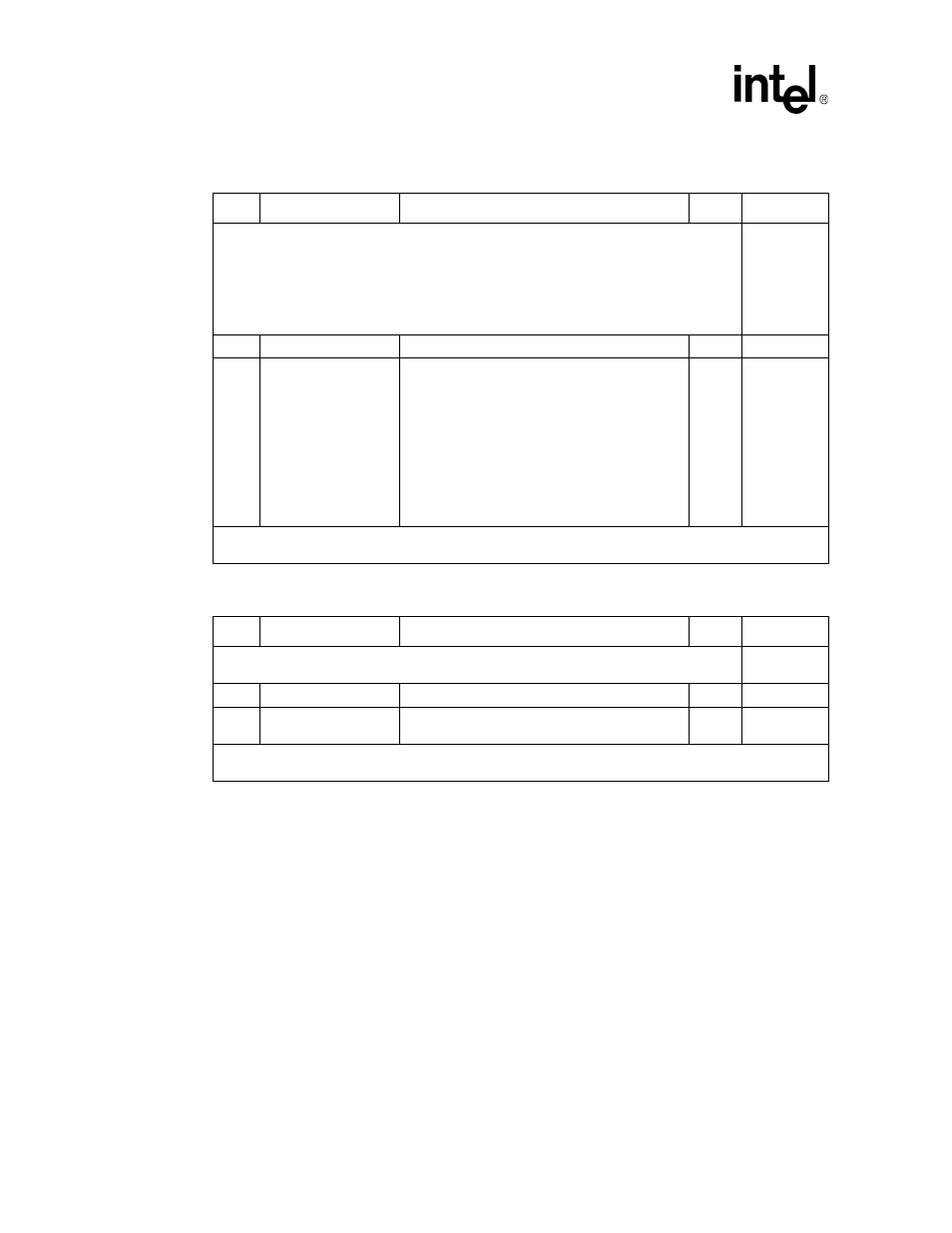

Table 82. MAC IF Mode and RGMII Speed ($ Port_Index + 0x10)

Bit

Name

Description

Type

1

Default

Register Description – MAC IF Mode: Determines the MAC operation frequency and mode

per port.

Changes to the data setting of this register must be made in conjunction with the

Interface Mode Change Enable Ports 0 - 3 ($0x794)"

to ensure a safe transition to a new

operational mode. Changes to this register must follow a proper sequence. Refer to

6.1, “Change Port Mode Initialization Sequence” on page 130

for the proper sequence for

changing the port mode and speed.

0x00000003

31:3

Reserved

Reserved

R

0x00000000

2:0

Port Mode

These bits are used to define the clock mode and

the RGMII/GMII mode of operation.

000 = Reserved

001 = Reserved

010 = GMII 1000 Mbps operation

011 = Reserved

100 = RGMII 10 Mbps operation

101 = RGMII 100 Mbps operation

11x = RGMII 1000 Mbps operation

R/W

011

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write

Table 83. Flush TX ($ Port_Index + 0x11)

Bit

Name

Description

Type

1

Default

Register Description: Used to flush all TX data. It is used if all traffic sent to a port should be

stopped.

0x00000000

31:1

Reserved

Reserved

R

0x00000000

0

Flush TX

This bit flushes all TX data and is used if all the

traffic sent to a port should be stopped.

R/W

0

1. RO = Read Only, No clear on Read; R = Read, Clear on Read; W = Write only; R/W = Read/Write, No

clear; R/W/C = Read/Write, Clear on Write