2 pipeline operation and interrupt processing, Pipeline operation and interrupt processing – FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 79

55

CHAPTER 5 PRECAUTIONARY INFORMATION FOR THE FR FAMILY CPU

5.2

Pipeline Operation and Interrupt Processing

The FR family CPU processes all instructions through pipeline operation. Therefore,

particularly for instructions that start hardware events, it is possible for contradictory

conditions to exist before and after an instruction.

■

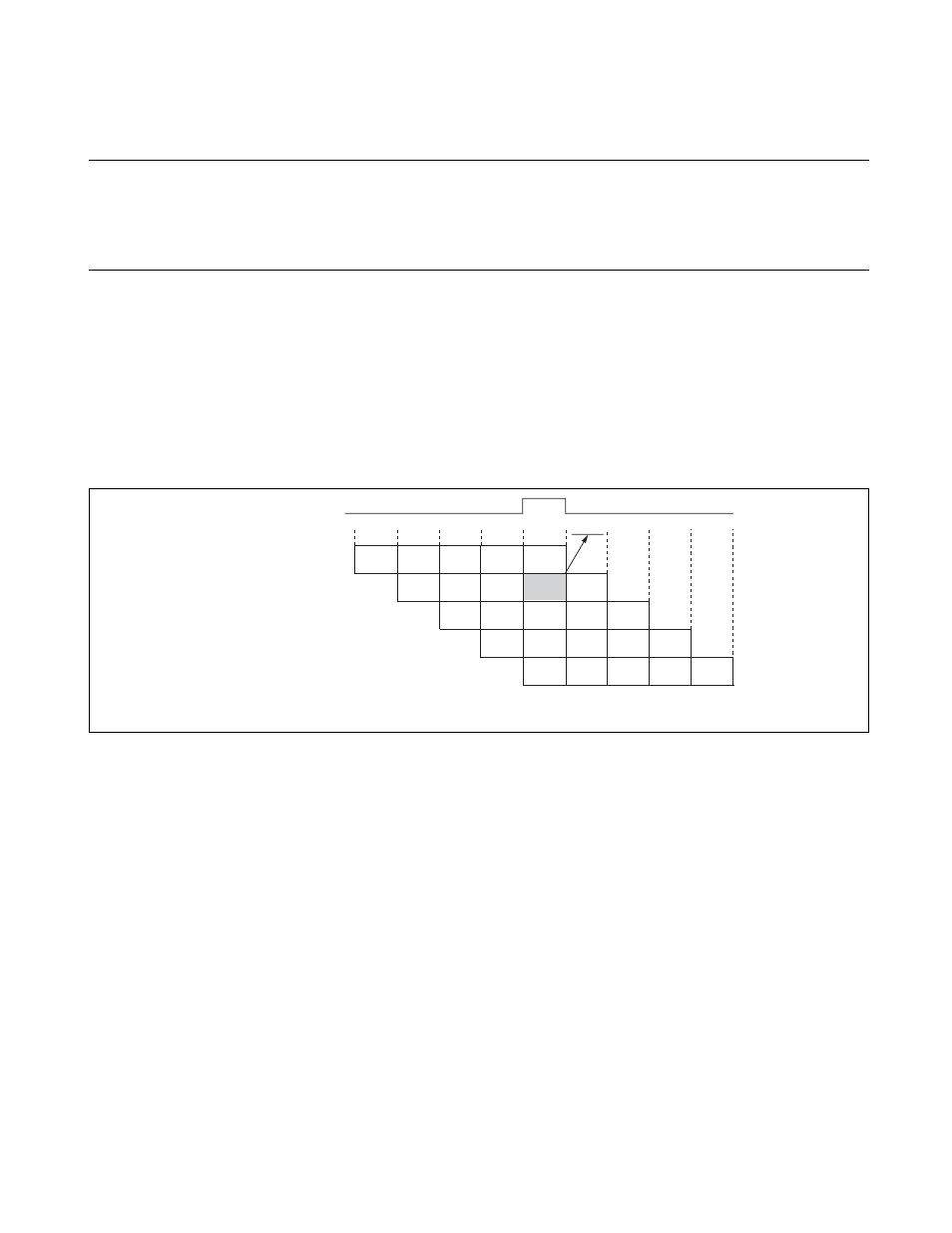

Precautionary Information for Interrupt Processing in Pipeline Operation

Because the FR family CPU operates in pipeline mode, the recognition of an interrupt signal is preceded by

several instructions in respective states of pipeline processing. If one of those instructions being executed in

the pipeline acts to delete the interrupt, the CPU will branch normally to the respective interrupt processing

program but when control is transferred to interrupt processing the interrupt request will no longer be

effective.

Note that this type of condition does not occur in exception or trap processing.

Figure 5.2-1 Example: Interrupt Accepted and Deleted Causing Mismatched Pipeline Conditions

■

Conditions that Are Actually Generated

The following processing conditions may cause an interrupt to be deleted after acceptance.

•

A program that clears interrupt sources while in interrupt-enabled mode

•

Writing to an interrupt-enable bit in a peripheral function while in interrupt-enabled mode

■

How to Avoid Mismatched Pipeline Conditions

To avoid deleting interrupts that have already been accepted, programmers should use the "I" flag in the

condition code register (CCR) in the program status (PS) to regulate interrupt sources.

IF

ID

EX

MA

WB

IF

ID

EX

MA

WB

IF

ID

--

--: Canceled stages

--

--

--

--

--

--

IF

IF

ID

EX

MA

WB

LD @R10, R1

Interrupt request

ADD R1, R3(cancelled)

BNE TestOK(cancelled)

EIT sequence execution #1

ST R2, @R11

None None None None

None None None

Generated Deleted