1 pipeline operation, Pipeline operation – FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 78

54

CHAPTER 5 PRECAUTIONARY INFORMATION FOR THE FR FAMILY CPU

5.1

Pipeline Operation

The FR family CPU processes all instructions using a 5-stage pipeline operation. This

makes it possible to process nearly all instructions within one cycle.

■

Overview of Pipeline Operation

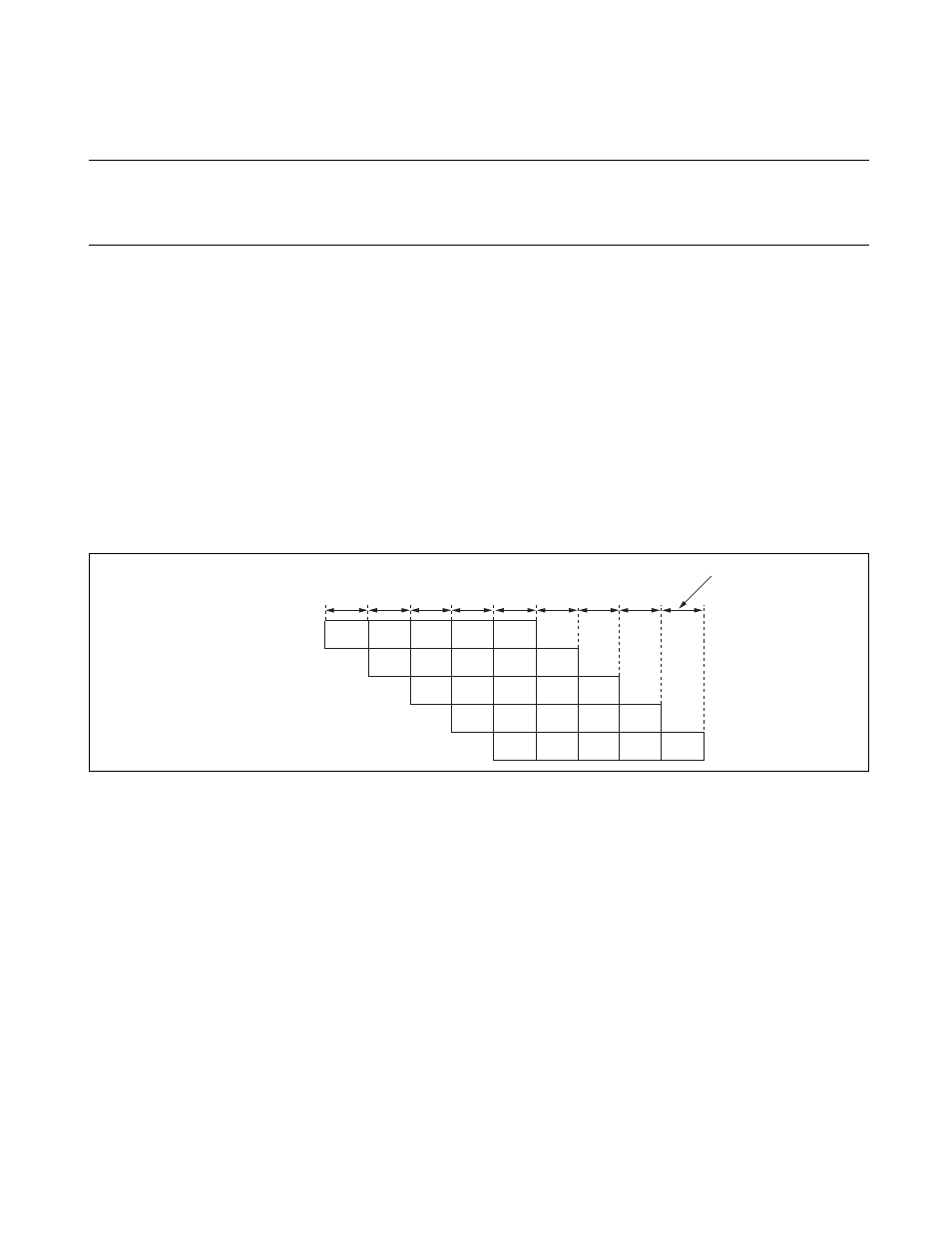

In a pipeline operation the steps by which the CPU interprets and executes instructions are divided into

several cycles, so that instructions can be processed simultaneously in successive cycles. This enables the

system to appear to execute in one cycle many instructions that would require several cycles in other

methods of processing. The FR family CPU simultaneously executes five types (IF, ID, EX, MA, and WB)

of processing cycles, as shown in Figure 5.1-1. This is referred to as five-stage pipeline processing.

•

IF:

Load instruction

•

ID:

Interpret instruction

•

EX:

Execute instruction

•

MA:

Memory access

•

WB:

Write to register

Figure 5.1-1 Example of Pipeline Operation in the FR Family CPU

●

Processes occurring in each 1 cycle in the above example:

(1) Load instruction "LD @R10,R1"

(2) Interpret instruction "LD @R10,R1" Load instruction "LD, @R11,R2"

(3) Execute instruction "LD @R10,R1" Interpret instruction "LD, @R11,R2"

Load instruction, "ADD R1, R3"

(4) Memory access instruction "LD @R10,R1" Execute instruction "LD, @R11,R2"

Interpret instruction, "ADD R1, R3" Load instruction "BNE:D TestOK"

(5) Write instruction "LD @R10,R1" to register Memory access instruction "LD, @R11,R2"

Execute instruction, "ADD R1, R3" Interpret instruction, "BNE:D TestOK"

Load instruction "ST R2,@R12"

(1)

(2)

(3)

(4)

(5)

IF

ID

EX

MA

WB

IF

ID

EX

MA

WB

IF

ID

EX

MA

WB

IF

ID

EX

MA

WB

IF

ID

EX

MA

WB

1 cycle

LD @R10, R1

LD @R11, R2

ADD R1, R3

BNE:D TestOK

ST R2, @R12