FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 112

88

CHAPTER 7 DETAILED EXECUTION INSTRUCTIONS

7.16

ANDH (And Half-word Data of Source Register to Data in

Memory)

Takes the logical AND of the half-word data at memory address "Ri" and the half-word

data in "Rj", stores the results to the memory address corresponding to "Ri".

The CPU will not accept hold requests between the memory read operation and the

memory write operation of this request.

■

ANDH (And Half-word Data of Source Register to Data in Memory)

Assembler format:

ANDH Rj, @Ri

Operation:

(Ri) and Rj

→

(Ri)

Flag change:

N:

Set when the MSB (bit 15) of the operation result is "1", cleared when the MSB is "0".

Z:

Set when the operation result is "0", cleared otherwise.

V and C: Unchanged

Execution cycles:

1 + 2a cycles

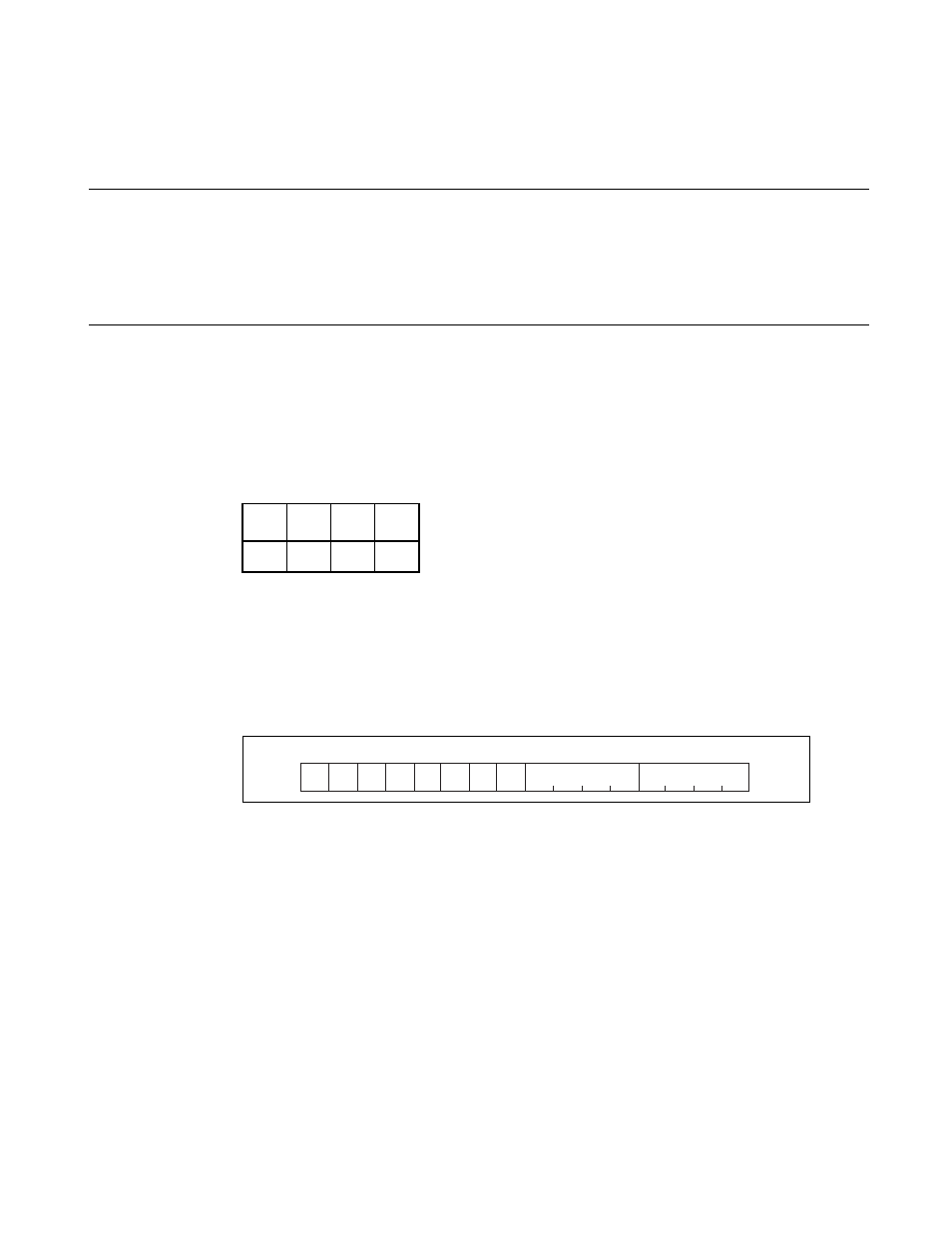

Instruction format:

N

Z

V

C

C

C

–

–

MSB

LSB

1

0

0

0

0

1

0

1

Rj

Ri

- T2000 (30 pages)

- SPARC ENTERPRISE M3000 (212 pages)

- PRIMERGY RX600 S6 (134 pages)

- BS2000 (37 pages)

- BX900 S1 (142 pages)

- BX900 S1 (144 pages)

- PRIMEQUEST 1000 Series C122-E119EN (109 pages)

- T5120 (26 pages)

- SPARC ENTERPRISE M9000 (560 pages)

- DESKPOWER 2000 (50 pages)

- SPARC M4000 (376 pages)

- ServerView Respurce Orchestrator Virtual Edition V3.1.0 (247 pages)

- PRIMERGY MX130 S2 (256 pages)

- SPARC ENTERPRISE T5120 (58 pages)

- T5240 (28 pages)

- M4000 (310 pages)

- SPARC M4000/M5000 (76 pages)

- TX150 S3 (95 pages)

- SPARC T5220 (240 pages)

- M9000 (518 pages)

- ServerView Resource Orchestrator Cloud Edition V3.1.0 (180 pages)

- PRIMERGY BX600 S2 (173 pages)

- M Server M4000 (30 pages)

- Primergy RX200 S2 (307 pages)

- DESKPOWER P301 (56 pages)

- SPARC Enterprise Server M4000 (62 pages)

- SPARC M8000 (4 pages)

- PRIMERGY B120 (68 pages)

- C120-E361-04EN (36 pages)

- R630 (76 pages)

- 2000 (66 pages)

- T1000 (84 pages)

- Server TX200 S6 (126 pages)

- PRIMERGY BX600 S3 (164 pages)

- SPARC ENTERPRISE T5220 (34 pages)

- SPARC M3000 (56 pages)

- TX300 (122 pages)

- PRIMERGY BX600 (288 pages)

- DESKPOWER 6000 (105 pages)

- SPARC Enterprise Server M3000 (8 pages)

- SPARC Enterprise Server M3000 (202 pages)

- T850 (18 pages)

- T5440 (212 pages)

- Service View Resource Orchestrator Cloud Edition V3.0.0 (102 pages)