FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 295

271

APPENDIX A Instruction Lists

Notes:

•

The field "rel8" in the TYPE-D instruction format and the field "rel11" in the TYPE-F format have

the following relation to the values "label9" and "label12" in assembly notation.

label9

→

rel8=(label9 – PC – 2)/2

label12

→

rel11=(label12 – PC – 2)/2

•

Delayed branching instructions are always executed after the following instruction (the delay slot).

•

In order to occupy a delay slot, an instruction must satisfy either of the following conditions. Any

other instructions used in this position may not be executed according to definition.

- Instructions other than branching instructions, with the cycle (CYC) column showing the value

"1".

- Instructions with the cycle (CYC) column showing the value "a", "b", "c", or "d".

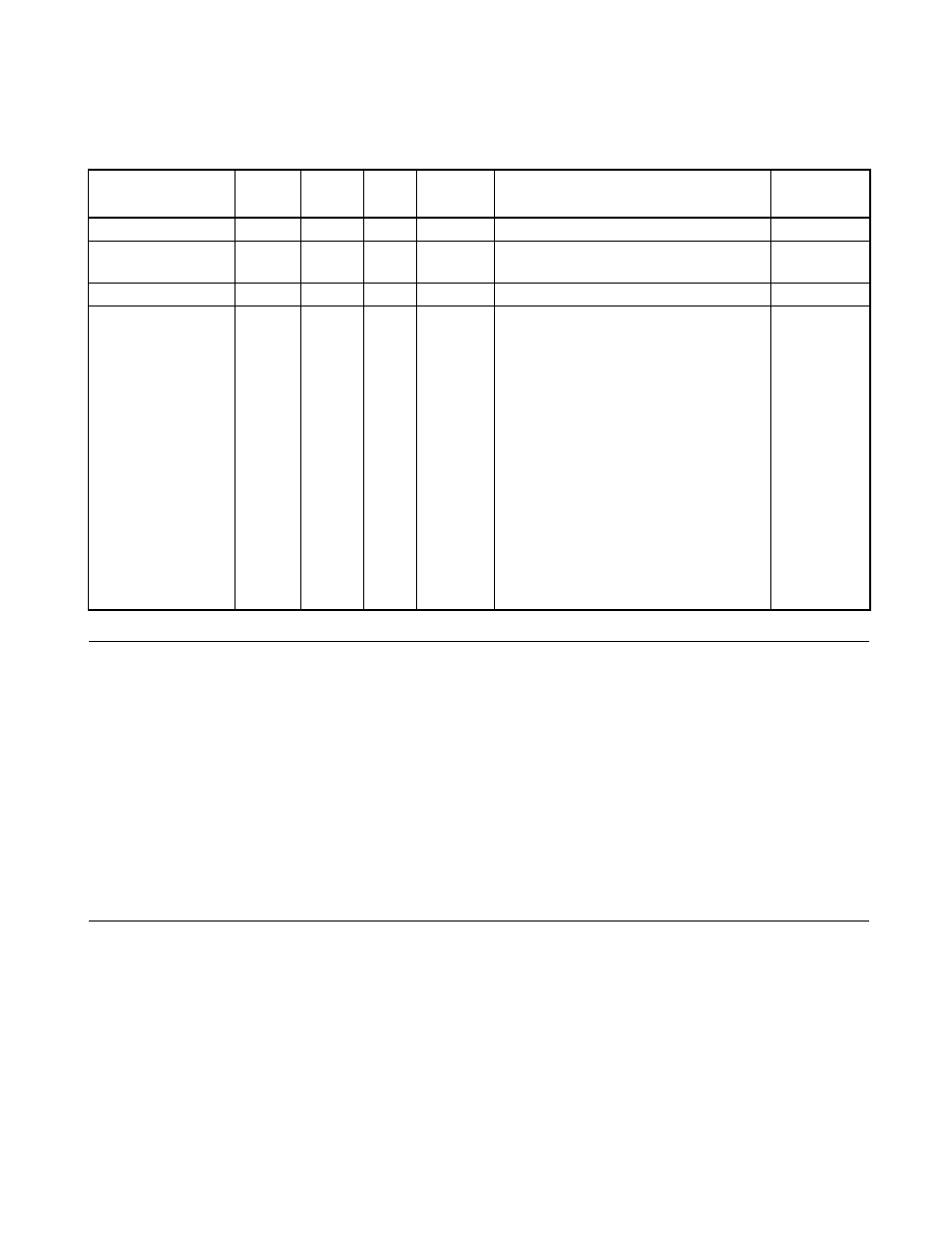

Table A.2-12 Delayed Branching Instructions (20 Instructions)

Mnemonic

Format

OP

CYC

FLAG

NZVC

Operation

Remarks

JMP:D @Ri

E

9F-0

1

– – – –

Ri

→ PC

CALL:D label12

CALL:D @Ri

F

E

D8

9F-1

1

1

– – – –

– – – –

PC+4

→ RP ,PC+2+rel11×2 → PC

PC+4

→ RP, Ri → PC

RET:D

E

9F-2

1

– – – –

RP

→ PC

Return

BNO:D label9

BRA:D label9

BEQ:D label9

BNE:D label9

BC:D label9

BNC:D label9

BN:D label9

BP:D label9

BV:D label9

BNV:D label9

BLT:D label9

BGE:D label9

BLE:D label9

BGT:D label9

BLS:D label9

BHI:D label9

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

F1

F0

F2

F3

F4

F5

F6

F7

F8

F9

FA

FB

FC

FD

FE

FF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

No branch

PC+2+rel8×2

→ PC

PC+2+rel8×2

→ PC if Z==1

PC+2+rel8×2

→ PC if Z==0

PC+2+rel8×2

→ PC if C==1

PC+2+rel8×2

→ PC if C==0

PC+2+rel8×2

→ PC if N==1

PC+2+rel8×2

→ PC if N==0

PC+2+rel8×2

→ PC if V==1

PC+2+rel8×2

→ PC if V==0

PC+2+rel8×2

→ PC if V xor N==1

PC+2+rel8×2

→ PC if V xor N==0

PC+2+rel8×2

→ PC if (V xor N) or Z==1

PC+2+rel8×2

→ PC if (V xor N) or Z==0

PC+2+rel8×2

→ PC if C or Z==1

PC+2+rel8×2

→ PC if C or Z==0