FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 297

273

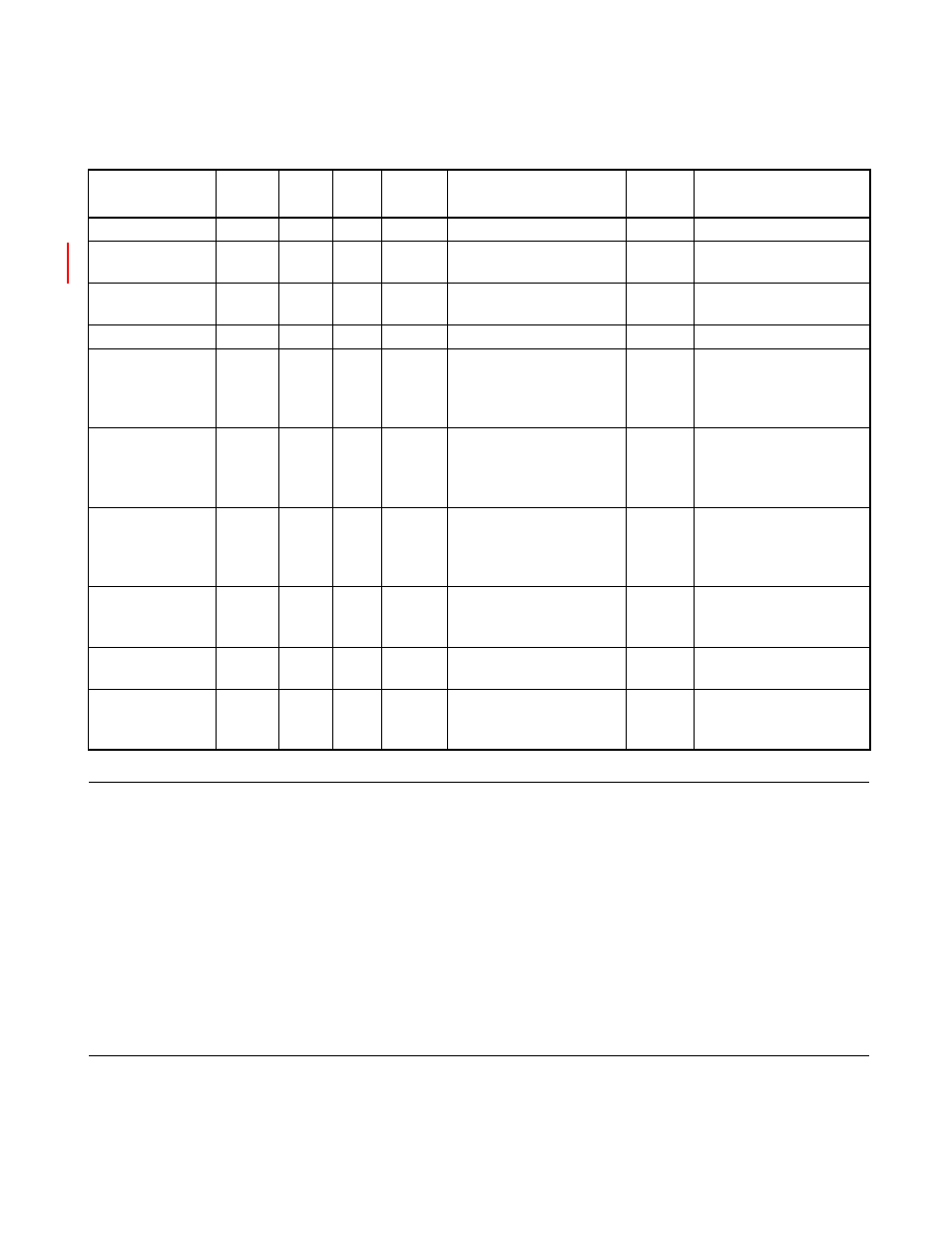

APPENDIX A Instruction Lists

Notes:

•

In the "ADD SP" instruction, the field "s8" in the TYPE-D instruction format has the following

relation to the value "s10" in assembly notation.

s10

→

s8=s10 >> 2

•

In the "ENTER" instruction, the field "u8" in the TYPE-D instruction format has the following

relation to the value "u10" in assembly notation.

u10

→

u8=u10 >> 2

•

The number of execution cycles for the "LDM0" (reglist) and "LDM1" (reglist) instructions is:

a × (n – 1) + b + 1 cycles, where "n" is the number of registers designated.

•

The number of execution cycles for the "STM0" (reglist) and "STM1" (reglist) instructions is:

a × n+1 cycles, where "n" is the number of registers designated.

Table A.2-16 Other Instructions (16 Instructions)

Mnemonic

Format

OP

CYC

FLAG

NZVC

Operation

RMW

Remarks

NOP

E

9F-A

1

– – – –

No change

-

ANDCCR #u8

ORCCR #u8

D

D

83

93

c

c

CCCC

CCCC

CCR and u8

→ CCR

CCR or u8

→ CCR

-

-

STILM #u8

D

87

1

– – – –

u8

→ ILM

-

Sets "ILM" immediate

value

ADDSP #s10

D

A3

1

– – – –

R15 += s10

-

"ADD SP" instruction

EXTSB Ri

EXTUB Ri

EXTSH Ri

EXTUH Ri

E

E

E

E

97-8

97-9

97-A

97-B

1

1

1

1

– – – –

– – – –

– – – –

– – – –

Sign extension 8

→ 32bit

Zero extension 8

→ 32bit

Sign extension 16

→ 32bit

Zero extension 16

→ 32bit

-

-

-

-

LDM0 (reglist)

LDM1 (reglist)

D

D

8C

8D

See

notes

below.

– – – –

– – – –

(R15)

→ reglist,

increment R15

(R15)

→ reglist,

increment R15

-

-

Load multiple R0 to R7

Load multiple R8 to R15

STM0 (reglist)

STM1 (reglist)

D

D

8E

8F

See

notes

below.

– – – –

– – – –

Decrement R15

reglist

→ (R15)

Decrement R15

reglist

→ (R15)

-

-

Store multiple R0 to R7

Store multiple R8 to R15

ENTER #u10

D

0F

1+a

– – – –

R14

→ (R15 – 4),

R15 – 4

→ R14,

R15 – u10

→ R15

-

Function entry processing

LEAVE

E

9F-9

b

– – – –

R14 + 4

→ R15,

(R15 – 4)

→ R14

-

Function exit processing

XCHB @Rj, Ri

A

8A

2a

– – – –

Ri

→ TEMP

(Rj)

→ Ri

TEMP

→ (Rj)

❍

Byte data for semaphore

processing