FUJITSU FR family 32-bit microcontroller instruction manuel CM71-00101-5E User Manual

Page 294

270

APPENDIX A Instruction Lists

Notes:

•

The field "rel8" in the TYPE-D instruction format and the field "rel11" in the TYPE-F format have

the following relation to the values "label9" and "label12" in assembly notation.

label9

→

rel8=(label9 – PC – 2)/2

label12

→

rel11=(label12 – PC – 2)/2

•

The value "2/1" in the cycle(CYC) column indicates "2" cycles if branching, "1" if not branching.

•

It is necessary to set the S flag to "0" for RETI execution.

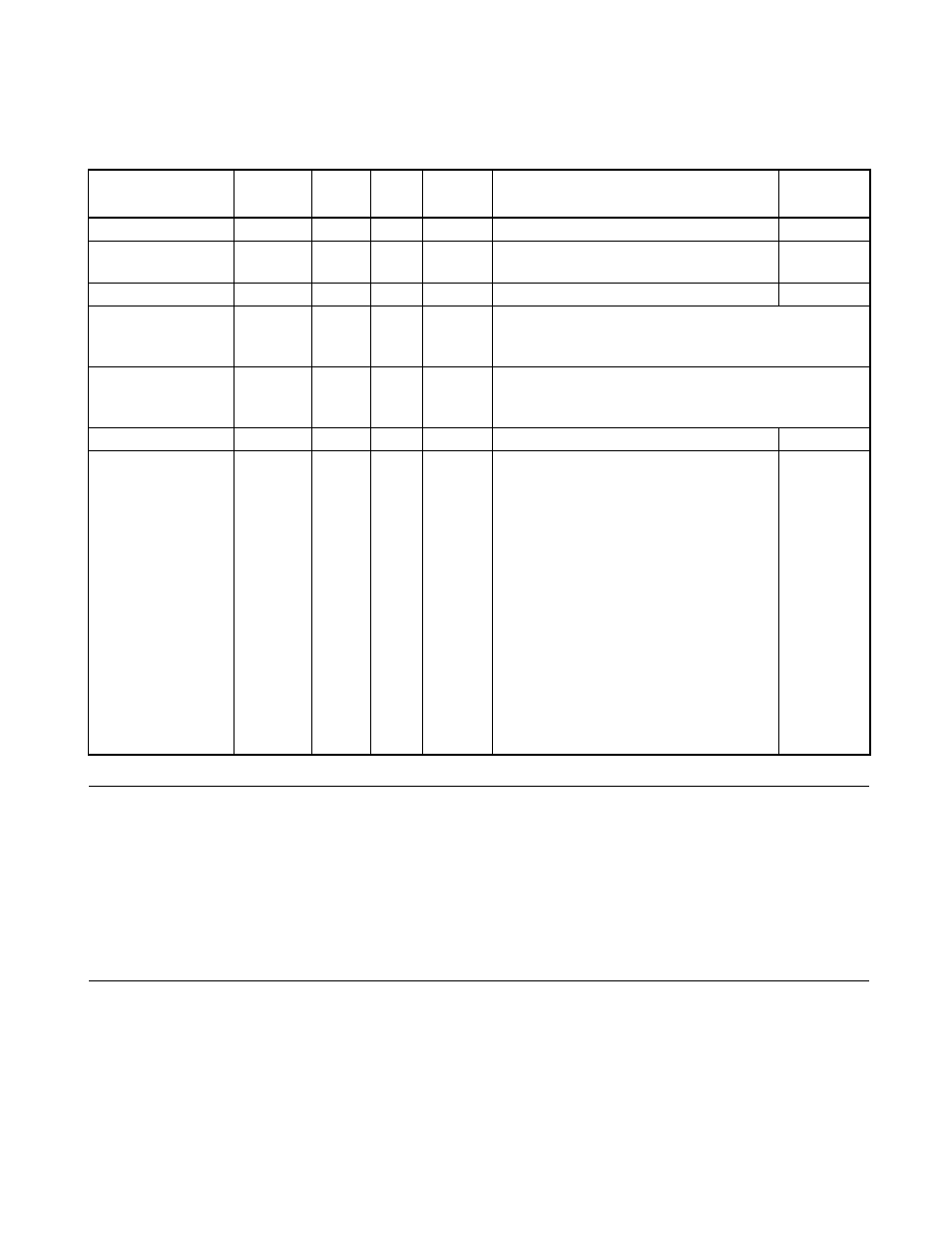

Table A.2-11 Non-delayed Branching Instructions (23 Instructions)

Mnemonic

Format

OP

CYC

FLAG

NZVC

Operation

Remarks

JMP @Ri

E

97-0

2

– – – –

Ri

→ PC

CALL label12

CALL @Ri

F

E

D0

97-1

2

2

– – – –

– – – –

PC+2

→ RP ,PC+2+rel11×2 → PC

PC+2

→ RP, Ri → PC

RET

E

97-2

2

– – – –

RP

→ PC

Return

INT #u8

D

1F

3+3a

– – – –

SSP–=4,PS

→ (SSP),SSP–=4,PC+2 → (SSP),

0

→ I flag, 0 → S flag,

(TBR+3FC–u8×4)

→ PC

INTE

E

9F-3

3+3a

– – – –

SSP–=4,PS

→ (SSP),SSP–=4,PC+2 → (SSP),

0

→ S flag, 4 → ILM,

(TBR+3D8–u8×4)

→ PC

RETI

E

97-3

2+2a

CCCC

(R15)

→ PC,R15+=4,(R15) → PS,R15+=4

BNO label9

BRA label9

BEQ label9

BNE label9

BC label9

BNC label9

BN label9

BP label9

BV label9

BNV label9

BLT label9

BGE label9

BLE label9

BGT label9

BLS label9

BHI label9

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

E1

E0

E2

E3

E4

E5

E6

E7

E8

E9

EA

EB

EC

ED

EE

EF

1

2

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

2/1

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

– – – –

No branch

PC+2+rel8×2

→ PC

PC+2+rel8×2

→ PC if Z==1

PC+2+rel8×2

→ PC if Z==0

PC+2+rel8×2

→ PC if C==1

PC+2+rel8×2

→ PC if C==0

PC+2+rel8×2

→ PC if N==1

PC+2+rel8×2

→ PC if N==0

PC+2+rel8×2

→ PC if V==1

PC+2+rel8×2

→ PC if V==0

PC+2+rel8×2

→ PC if V xor N==1

PC+2+rel8×2

→ PC if V xor N==0

PC+2+rel8×2

→ PC if (V xor N) or Z==1

PC+2+rel8×2

→ PC if (V xor N) or Z==0

PC+2+rel8×2

→ PC if C or Z==1

PC+2+rel8×2

→ PC if C or Z==0