Yaskawa MP900 Series Machine Controller New Ladder Editor User Manual

Page 153

1.7 DDC Instructions

1-143

1

Here, the LLAG operation is expressed as follows:

The following operation is performed within the LLAG instruction with dt

= Ts, dY = Y-Y’,

and dX

= X-X’

Y

= 0, REM = 0, X = 0, are output when the LLAG reset (RST) is "ON".

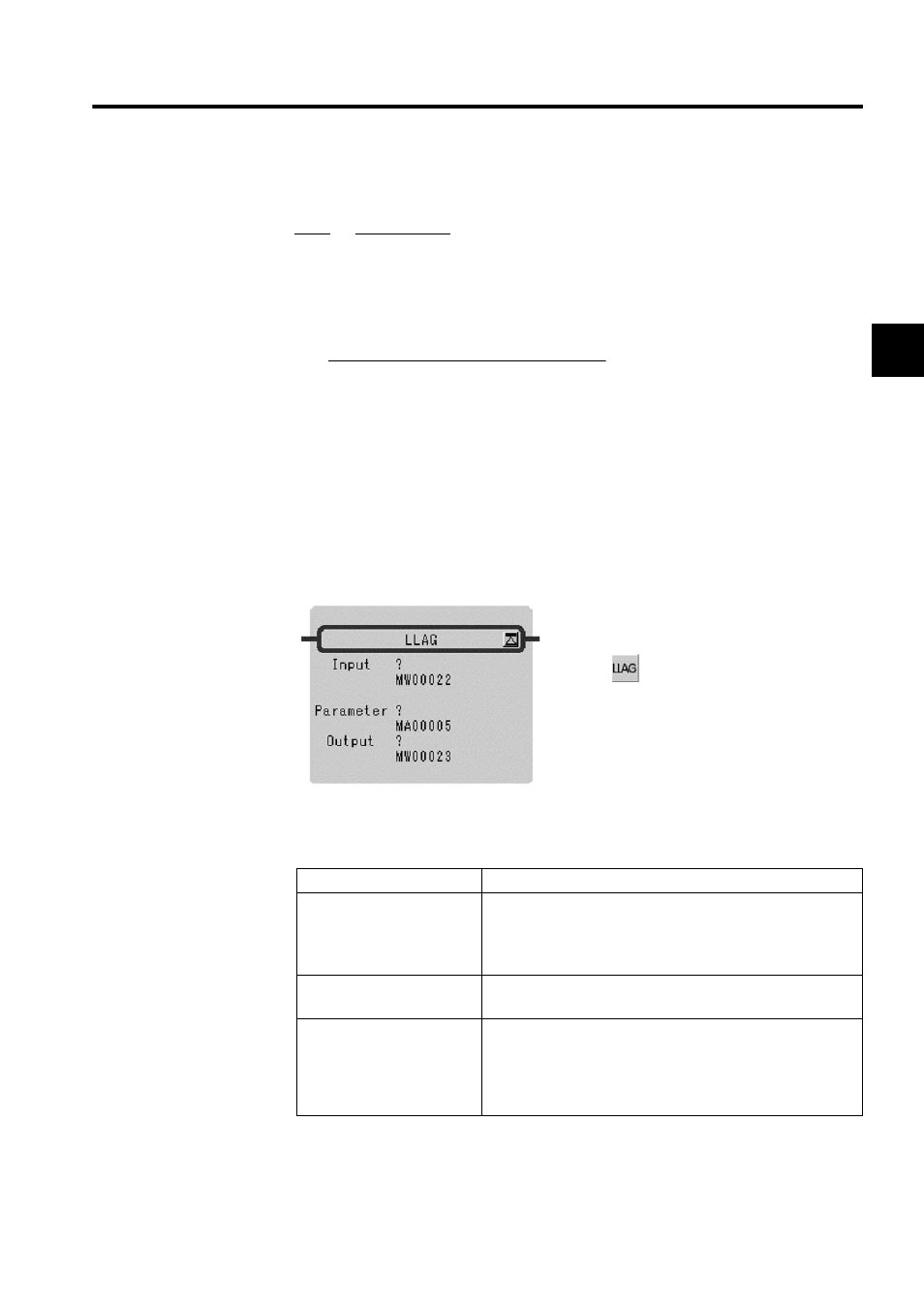

Format

Parameter

Parameter Name

Setting

Input

• Any integer type and real number type register

• Any integer type and real number type register with subscript

• Subscript register

• Constant

Parameter

• Register address (except for # and C registers)

• Register address with subscript (except for # and C registers)

Output

• Any integer type and real number type register (except for #

and C registers)

• Any integer type and real number type register with subscript

(except for # and C registers)

• Subscript register

Y

1 + T2

× S

X

=

1 + T1

× S

;

ie. T

× (dY/dt) + Y = T2 × (dX/dt) + X

T1

× Y + (T2 + Ts) ×X

–

T2

×X + REM

Y =

T1 + Ts

X: input value

Y: output value

X : previous input value

Y : previous output value

Ts: scan time setting

,

,

,

,

Symbol: LLAG

Full Name: Phase Lead Lag

Category: DDC

Icon: