8 phase lead/lag instruction (llag), Outline – Yaskawa MP900 Series Machine Controller New Ladder Editor User Manual

Page 152

1 Ladder Program Instructions

1.7.8 PHASE LEAD/LAG Instruction (LLAG)

1-142

1.7.8 PHASE LEAD/LAG Instruction (LLAG)

Outline

The LLAG instruction calculates the phase lead/lag according to the contents of a previously

set parameter table. The input (Input) to the LLAG operation must be integer or real number

data.

Double-length integer data cannot be used. The configurations of the parameter tables for

integer and real number data are different. Operations are performed by processing each

parameter as an integer consisting of the lower-place 16 bits.

* Relay I/O Bit Assignment

* Relay I/O Bit Assignment

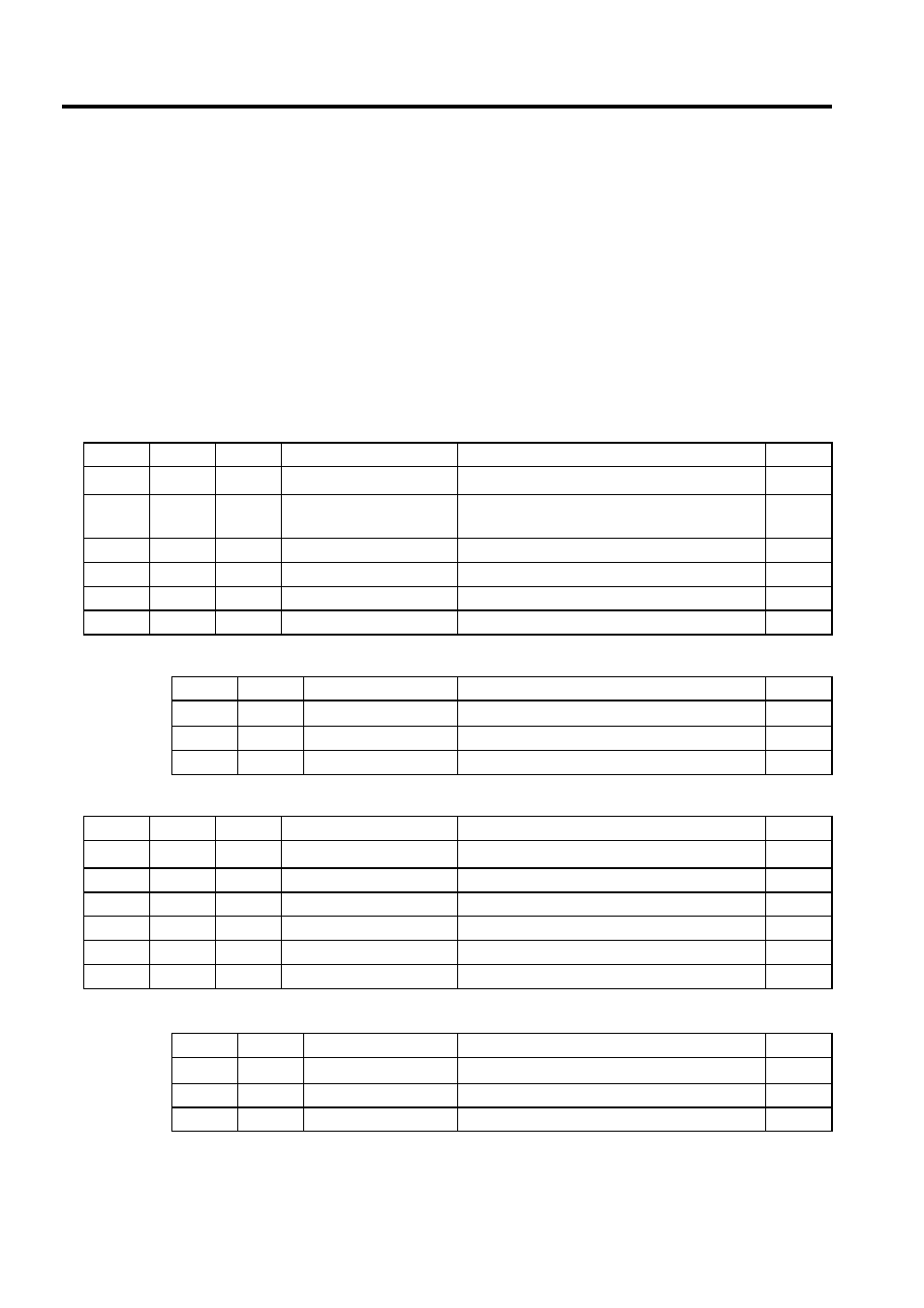

Table 1.20 Integer Type LLAG Instruction Parameters

ADR

Type

Symbol

Name

Specifications

I/O

0

W

RLY

Relay I/O

Relay input, relay output

∗

IN/OUT

1

W

T2

Phase lead time

constant

Phase lead time constant (ms)

IN

2

W

T1

Phase lag time constant

Phase lag time constant (ms)

IN

3

W

Y

LLAG output

LLAG output (may also be output to the A register)

OUT

4

W

REM

Remainder

Remainder stored

OUT

5

W

X

Input stored

Input value stored

OUT

BIT

Symbol

Name

Specifications

I/O

0

IRST

LLAG reset

"ON" is input when LLAG is reset.

IN

1 to 7

−

(Reserved)

Reserved relay for input

IN

8 to F

−

(Reserved)

Reserved relay for output

OUT

Table 1.21 Real Number Type LLAG Instruction Parameters

ADR

Type

Symbol

Name

Specifications

I/O

0

W

RLY

Relay I/O

Relay input, relay output

∗

IN/OUT

1

W

−

(Reserved)

Reserved register

−

2

W

T2

Phase lead time constant

Phase lead time constant (s)

IN

4

W

T1

Phase lag time constant

Phase lag time constant (s)

IN

6

W

Y

LLAG output

LLAG output (may also be output to the F register)

OUT

8

W

X

Input preservation

Input value stored

OUT

BIT

Symbol

Name

Specifications

I/O

0

IRST

LLAG reset

"ON" is input when LLAG is reset.

IN

1 to 7

−

(Reserved)

Reserved relay for input

IN

8 to F

−

(Reserved)

Reserved relay for output

OUT