2 standard event status register (esr), Standard event status register (esr) -2, Table 3-1 scpi status byte -2 – AMETEK M130 User Manual

Page 52

IEEE 488.2 and SCPI Command Operation

Sorensen Ethernet Option

3-2

M130/131 Programming Manual

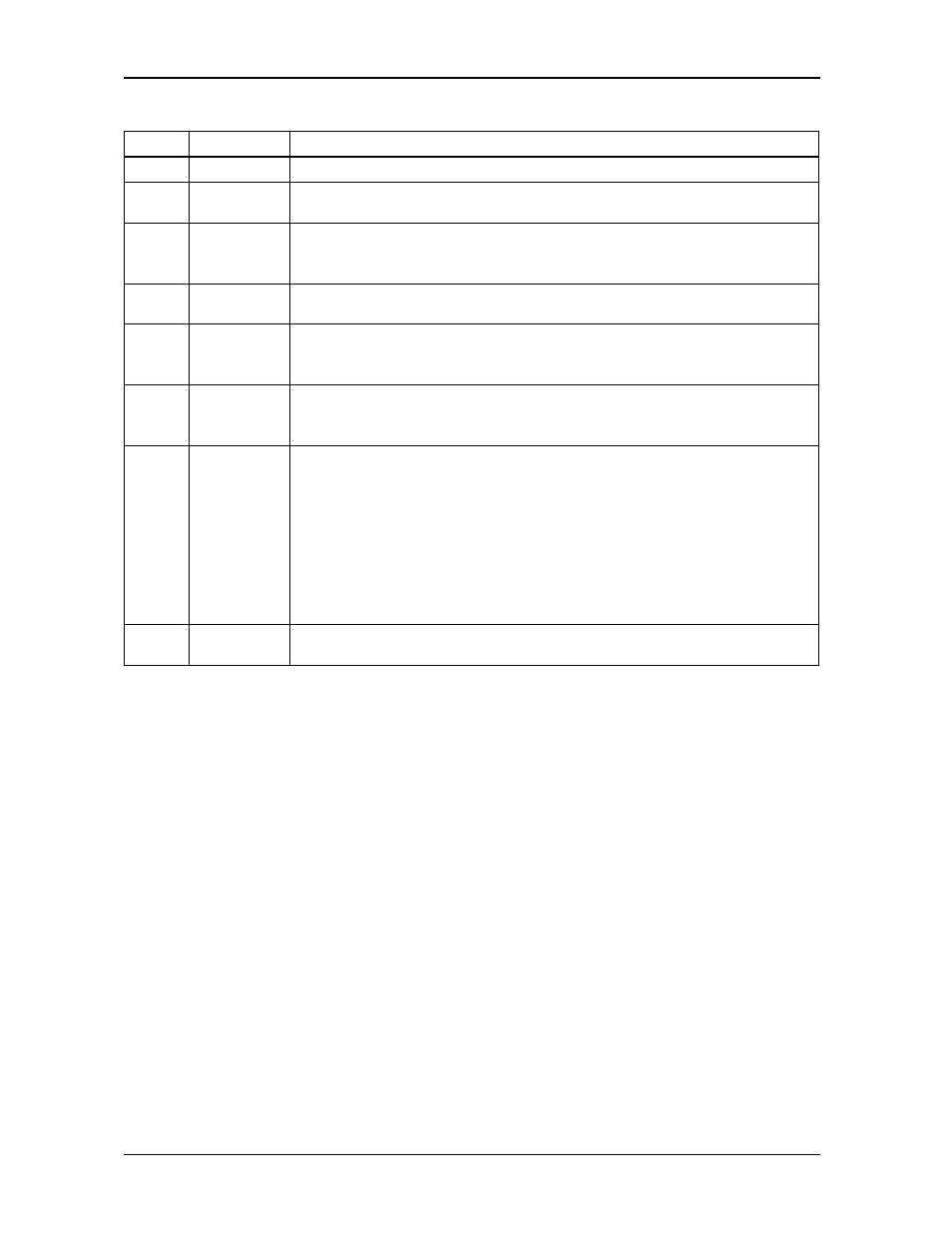

Table 3-1 SCPI Status Byte

Bit

Hex Value Description

0

0x01

Not used.

1

0x02

Protection Event Status flag. Indicates the selected protection

event occurred.

2

0x04

Error/event queue message available. Set when any error/event is

entered in the System Error Queue. It is read using the

SYSTem:ERRor? query.

3

0x08

Questionable Status flag. Indicates the quality of the current data

being acquired. This bit is not used.

4

0x10

Message available (MAV). Indicates a message is available in the

GPIB or Ethernet output queue. Cleared after the GPIB or Ethernet

output buffer is read.

5

0x20

Standard Event Status Register (ESR). Summary bit for the ESR.

Set when any of the ESR bits are set and cleared when the ESR is

read.

6

0x40

Request Service flag (RQS) for serial polling or Master Summary

Status (MSS) in response to *STB? If service requests are enabled

(with the *SRE command), this bit represents the RQS and will be

sent in response to a serial poll, then cleared. If RQS is not

enabled, the bit represents the MSS bit and indicates the device

has at least one reason to request service. Even though the device

sends the MSS bit in response to a status query (*STB?), it is not

sent in response to a serial poll. It is not considered part of the

IEEE-488.1 Status Byte.

7

0x80

Operation Status flag. Indicates the current operational state of the

unit. This bit is not used.

3.2.2

S

TANDARD

E

VENT

S

TATUS

R

EGISTER

(ESR)

• To read the Standard Event Status Register (ESR), use the *ESR?

command.

• To clear the ESR, either read this register or issue the *CLS command.

• To enable corresponding ESR bits to be summarized in the summary bit

of the SCPI Status byte, issue the *ESE (Standard Event Status Enable

Register) command.