1 svm and power control register descriptions, 1 power control register (pwcn, m0[0ch]), 1 svm and power control register descriptions -1 – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 96: 1 power control register (pwcn, m0[0ch]) -1, Maxq family user’s guide: maxq8913 supplement

MAXQ Family User’s Guide:

MAXQ8913 Supplement

23-1

SECTION 23: SUPPLY VOLTAGE MONITOR AND POWER CONTROL

(SPECIFIC TO MAXQ8913)

The MAXQ8913 provides a number of features to allow monitoring and control of its on-board power supplies. The sup-

ply voltage monitor register (SVM) monitors the DVDD power supply and can alert the processor through an interrupt

if DVDD falls below a programmable threshold. Other control bits allow the processor to reduce power consumption

and configure various aspects of clock operation.

The MAXQ8913 provides the following power monitoring and control features:

• SVM compares DVDD against a programmable threshold from approximately 2.7V to 3.5V.

• Optional SVM register interrupt can be triggered when DVDD drops below the programmed threshold.

• SVM interrupt can be used to trigger switchback or exit from stop mode.

• Internal 1.8V regulator can optionally be disabled in stop mode to conserve power.

• Brownout detection can optionally be disabled in stop mode to conserve power.

23.1 SVM and Power Control Register Descriptions

The following peripheral registers are used to control the supply voltage monitoring and power control functions.

Addresses for all registers are given as “Mx[yy],” where x is the module number (from 0 to 15 decimal) and yy is the

register index (from 00h to 1Fh hexadecimal). Fields in the bit definition tables are defined as follows:

• Name: Symbolic names of bits or bit fields in this register.

• Reset: The value of each bit in this register following a standard reset. If this field reads “unchanged,” the given bit

is unaffected by standard reset. If this field reads “s,” the given bit does not have a fixed 0 or 1 reset value because

its value is determined by another internal state or external condition.

• POR: If present this field defines the value of each bit in this register following a power-on reset (as opposed to a

standard reset). Some bits are unaffected by standard resets and are set/cleared by POR only.

• Access: Bits can be read-only (r) or read/write (rw). Any special restrictions or conditions that could apply when

reading or writing this bit are detailed in the bit description.

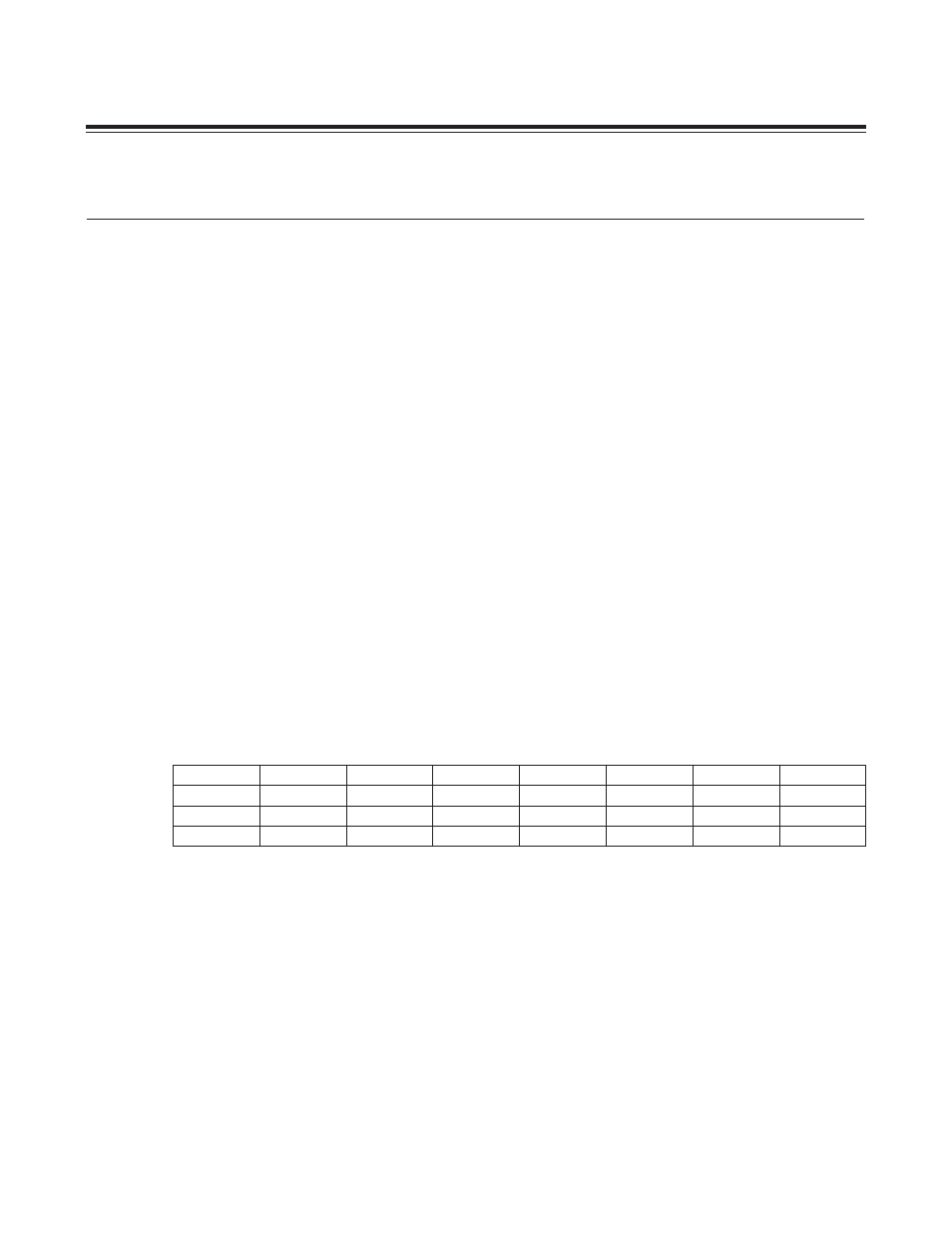

23.1.1 Power Control Register (PWCN, M0[0Ch])

Bit 7: Brownout-Detection Disable (BOD). This bit controls whether the brownout detection is enabled during stop

mode only and only when the internal 1.8V regulator is also disabled (REGEN = 0).

0 = Brownout detection is disabled during stop mode, if REGEN = 0.

1 = Brownout detection is enabled during stop mode.

Bit 6: Regulator Enable (REGEN). This bit controls whether the internal 1.8V regulator is enabled during stop mode

only. (The internal regulator is always enabled outside of stop mode.)

0 = The internal regulator is disabled during stop mode to conserve power.

1 = The internal regulator is enabled during stop mode.

Bits 5:1: Reserved. Read returns 0.

*HFXD can only be written to 1 when both RGSL = 1 and RGMD = 1 (running from ring oscillator).

Bit #

7

6

5

4

3

2

1

0

Name

BOD

REGEN

—

—

—

—

—

HFXD

Reset

No effect

No effect

No effect

No effect

No effect

No effect

No effect

No effect

POR

0

0

0

0

0

0

0

0

Access

rw

rw

r

r

r

r

r

rw*

Maxim Integrated