Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Maxq family user’s guide: maxq8913 supplement, Functional diagrams, Evaluation kit available

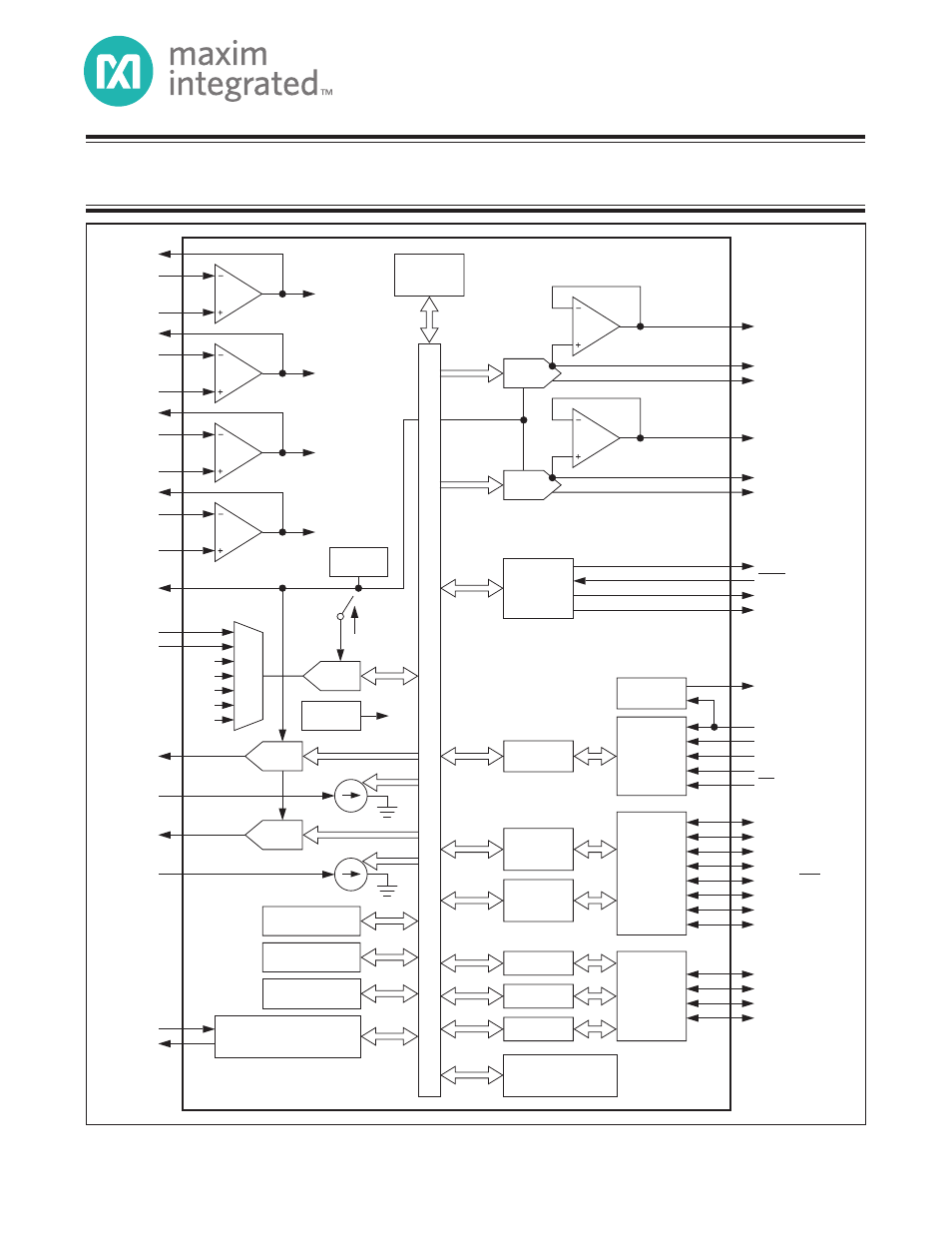

Functional Diagrams

Pin Configurations appear at end of data sheet.

Functional Diagrams continued at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct

at 1-888-629-4642, or visit Maxim’s website at www.maximintegrated.com.

EVALUATION KIT AVAILABLE

MAXQ FAMILY USER’S GUIDE:

MAXQ8913 SUPPLEMENT

Rev 0; 8/09

10-BIT

DAC

MAXQ8913

OUTA

AIN2

INA-

INA+

DAC1

RIN+

RIN-

OUTB

AIN3

INB-

INB+

OUTC

AIN4

INC-

INC+

OUTD

REFA

DAC3

AIN5

REF

AVDD

AIN6

CURRENT SINK

8-BIT

IND-

IND+

AIN0

AIN1

HFXIN

HFXOUT

SINK1

AIN2

AIN3

AIN4

AIN5

AIN6

12-BIT

SAR DAC

8-BIT DAC

1.5V

REFERENCE

MUX

TEMP

SENSOR

FLASH

64KB

SRAM

4KB

UTILITY ROM

4KB

CLOCK GENERATOR

RC OSC, HF CRYSTAL OSC,

1MHz RING OSC

DAC4

CURRENT SINK

8-BIT

SINK2

8-BIT DAC

MAXQ20

16-BIT RISC

CORE

CLASS

D-AMP

CONTROL

WATCHDOG

TIMER

POWER-ON

RESET,

BROWNOUT

MONITOR

1.8V CORE

LDO REG

AGND

JTAG

16 x 16

HARDWARE MULTIPLY

ACCUMULATE UNIT

4-WIRE

(SPI)

INTERFACE

PORT 0

AND

INTERRUPT

REG18

SYNCIN

FAULT

SHDNR

SHDNL

DVDD

DGND

AVDD

AGND

RST

P0.0/INT0/TCK

P0.1/INT1/TDI

P0.2/INT2/TMS

P0.3/INT3/TDO

P0.4/INT4/SSEL

P0.5/INT5/SCLK

P0.6/INT6/MOSI

P0.7/INT7/MISO

I

2

C

USART

TIMER B

PORT 1

AND

INTERRUPT

P1.0/INT8/SCL/TX

P1.1/INT9/SDA/RX

P1.2/INT10/TB0A

P1.3/INT11/TB0B

10-BIT

DAC

DAC2

LIN+

LIN-

Document Outline

- ADDENDUM TO SECTION 1: OVERVIEW

- ADDENDUM TO SECTION 2: ARCHITECTURE

- ADDENDUM TO SECTION 3: PROGRAMMING

- ADDENDUM TO SECTION 4: SYSTEM REGISTER DESCRIPTIONS

- ADDENDUM TO SECTION 5: PERIPHERAL REGISTER MODULES

- ADDENDUM TO SECTION 6: GENERAL-PURPOSE I/O MODULE

- 6.1 GPIO and External Interrupt Register Descriptions

- 6.1.1 Port 0 Direction Register (PD0, M0[10h])

- 6.1.2 Port 1 Direction Register (PD1, M0[11h])

- 6.1.3 Port 0 Input Disable Register (PID0, M0[0Dh])

- 6.1.4 Port 0 Output Register (PO0, M0[00h])

- 6.1.5 Port 1 Output Register (PO1, M0[01h])

- 6.1.6 Port 0 Input Register (PI0, M0[08h])

- 6.1.7 Port 1 Input Register (PI1, M0[09h])

- 6.1.8 External Interrupt Flag 0 Register (EIF0, M0[02h])

- 6.1.9 External Interrupt Flag 1 Register (EIF1, M0[04h])

- 6.1.10 External Interrupt Enable 0 Register (EIE0, M0[03h])

- 6.1.11 External Interrupt Enable 1 Register (EIE1, M0[05h])

- 6.1.12 External Interrupt Edge Select 0 Register (EIES0, M0[0Ah])

- 6.1.13 External Interrupt Edge Select 1 Register (EIES1, M0[0Bh])

- 6.2 Port Pin Examples

- 6.1 GPIO and External Interrupt Register Descriptions

- ADDENDUM TO SECTION 7: TIMER/COUNTER 0 MODULE

- ADDENDUM TO SECTION 8: TIMER/COUNTER 1 MODULE

- ADDENDUM TO SECTION 9: TIMER/COUNTER 2 MODULE

- ADDENDUM TO SECTION 10: SERIAL I/O MODULE

- ADDENDUM TO SECTION 11: SERIAL PERIPHERAL INTERFACE (SPI) MODULE

- ADDENDUM TO SECTION 12: HARDWARE MULTIPLIER MODULE

- ADDENDUM TO SECTION 13: 1-Wire BUS MASTER

- ADDENDUM TO SECTION 14: REAL-TIME CLOCK MODULE

- ADDENDUM TO SECTION 15: TEST ACCESS PORT (TAP)

- ADDENDUM TO SECTION 16: IN-CIRCUIT DEBUG MODE

- ADDENDUM TO SECTION 17: IN-SYSTEM PROGRAMMING (JTAG)

- 17.1 JTAG Bootloader Protocol

- 17.2 Family 0 Commands (Not Password Protected)

- 17.3 Family 1 Commands: Load Variable Length (Password Protected)

- 17.4 Family 2 Commands: Dump Variable Length (Password Protected)

- 17.5 Family 3 Commands: CRC Variable Length (Password Protected)

- 17.6 Family 4 Commands: Verify Variable Length (Password Protected)

- 17.7 Family 5 Commands: Load and Verify Variable Length (Password Protected)

- 17.8 Family E Commands: Erase Fixed Length (Password Protected)

- ADDENDUM TO SECTION 18: MAXQ FAMILY INSTRUCTION SET SUMMARY

- SECTION 19: ANALOG-TO-DIGITAL CONVERTER (SPECIFIC TO MAXQ8913)

- 19.1 Analog-to-Digital Converter Features

- 19.2 Analog-to-Digital Pins and Control Registers

- 19.2.1 Analog-to-Digital Converter Status Register (ADST, M4[06h])

- 19.2.2 ADC Conversion Sequence Address Register (ADADDR, M3[01h])

- 19.2.3 ADC Control Register (ADCN, M3[08h])

- 19.2.4 ADC Data Register (ADDATA, M3[09h])

- 19.2.5 ADC Data Buffer Registers (ADBUF[0] to ADBUF[15], ADDATA[00h] to ADDATA[0Fh])

- 19.2.6 ADC Conversion Configuration Registers (ADCFG[0] to ADCFG[7], ADDATA[10h] to ADDATA[17h])

- 19.2.7 Temperature Sensor Enable Register (TEMPEN, M3[0Ch])

- 19.3 Analog-to-Digital Converter Code Examples

- SECTION 20: DIGITAL-TO-ANALOG CONVERTERS (SPECIFIC TO MAXQ8913)

- SECTION 21: TIMER/COUNTER B MODULE (SPECIFIC TO MAXQ8913)

- 21.1 Timer/Counter B Register Descriptions

- 21.2 Timer/Counter B Operation

- 21.2.1 Timer B 16-Bit Timer/Counter Mode with Autoreload

- 21.2.2 Timer B 16-Bit Capture Mode

- 21.2.3 Timer B 16-Bit Up/Down Count with Autoreload Mode

- 21.2.4 Timer B Clock Output Mode

- 21.2.5 Timer B PWM/Output Control Functionality

- 21.2.6 16-Bit Up Count PWM/Output Control Mode

- 21.2.7 16-Bit Up/Down Count PWM/Output Control Mode

- 21.2.8 EXENB Control During PWM/Output Control Mode

- 21.3 Timer B Examples

- SECTION 22 : I2C BUS INTERFACE (SPECIFIC TO MAXQ8913)

- 22.1 I2C Register Descriptions

- 22.1.1 I2C Data Buffer Register (I2CBUF, M1[06h])

- 22.1.2 I2C Status Register (I2CST, M3[01h])

- 22.1.3 I2C Interrupt Enable Register (I2CIE, M1[07h])

- 22.1.4 I2C Control Register (I2CCN, M1[04h])

- 22.1.5 I2C Clock Control Register (I2CCK, M1[0Ch])

- 22.1.6 I2C Timeout Register (I2CTO, M1[0Dh])

- 22.1.7 I2C Slave Address Register (I2CSLA, M1[0Eh])

- 22.2 I2C Code Examples

- 22.1 I2C Register Descriptions

- SECTION 23: SUPPLY VOLTAGE MONITOR AND POWER CONTROL(SPECIFIC TO MAXQ8913)

- SECTION 24: INPUT/OUTPUT AMPLIFIERS (SPECIFIC TO MAXQ8913)

- SECTION 25: UTILITY ROM (SPECIFIC TO MAXQ8913)

- APPENDIX 1: MAXQ8913 DEVICE INCLUDE FILE FOR MAX-IDE

- REVISION HISTORY