Addendum to section 6: general-purpose i/o module, Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 33

MAXQ Family User’s Guide:

MAXQ8913 Supplement

6-1

ADDENDUM TO SECTION 6: GENERAL-PURPOSE I/O MODULE

The MAXQ8913 provides up to 12 port pins for general-purpose I/O that are grouped into logical ports P0 and P1. Each

of these port pins has the following features:

• CMOS output drivers

• Schmitt trigger inputs

• Optional weak pullup to DVDD when operating in input mode

For the eight GPIO pins located in port 0 (P0.0 to P0.7) the Schmitt trigger inputs can be explicitly disabled on a pin-

by-pin basis by setting bits in the PID0 register.

Many of the port pins on the MAXQ8913 are also multiplexed with special and alternate functions as listed below.

All these functions are disabled by default with the exception of the debug port interface pins, which are enabled by

default following any reset. The behavior of these functions breaks down into two overall categories.

• Special functions override the PD and PO settings for the port pin when they are enabled. Once the special func-

tion takes control, normal control of the port pin is lost until the special function completes its task or is disabled.

Examples of special functions include serial port transmit and I

2

C clock and data.

• Alternate functions operate in parallel with the PD and PO settings for the port pin, and generally consist of input-

only functions such as external interrupts. When an alternate function is enabled for a port pin, the port pin’s output

state is still controlled in the usual manner.

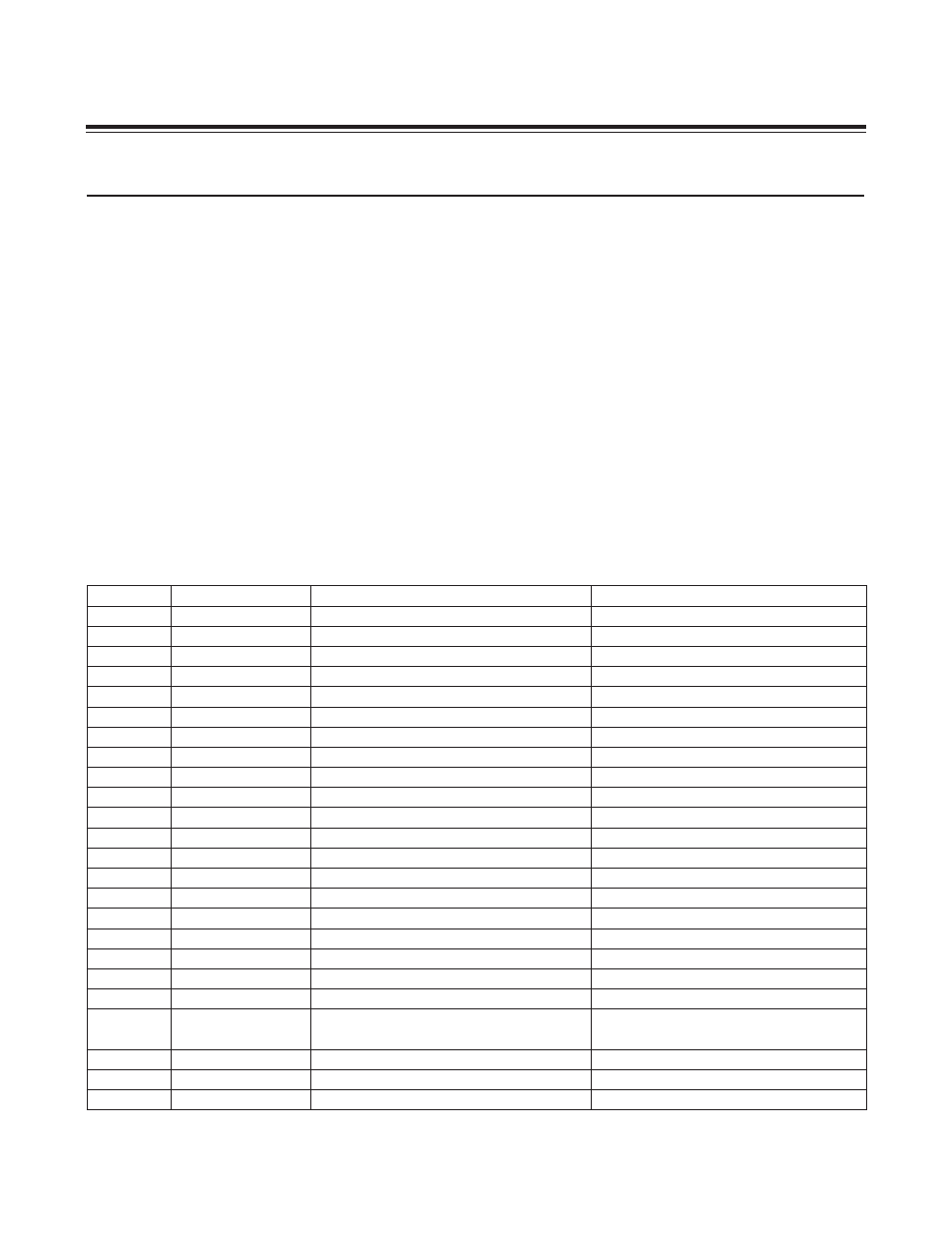

Table 6-1. Port Pin Special and Alternate Functions

PORT PIN

FUNCTION TYPE

FUNCTION

ENABLED WHEN

P0.0

Alternate

External Interrupt 0

(EIE0.0) EX0 = 1

P0.0

Alternate

JTAG Interface—TAP Clock (TCK)

(SC.7) TAP = 1

P0.1

Alternate

External Interrupt 1

(EIE0.1) EX1 = 1

P0.1

Alternate

JTAG Interface—TAP Data Input (TDI)

(SC.7) TAP = 1

P0.2

Alternate

External Interrupt 2

(EIE0.2) EX2 = 1

P0.2

Alternate

JTAG Interface—TAP Mode Select (TMS)

(SC.7) TAP = 1

P0.3

Alternate

External Interrupt 3

(EIE0.3) EX3 = 1

P0.3

Special

JTAG Interface—TAP Data Output (TDO)

(SC.7) TAP = 1

P0.4

Alternate

External Interrupt 4

(EIE0.4) EX4 = 1

P0.4

Alternate

SPI Slave Select Input (SSEL)

SPIEN = 1 and MSTM = 0

P0.5

Alternate

External Interrupt 5

(EIE0.5) EX5 = 1

P0.5

Alternate

SCLK—SPI Clock Input (Slave Mode)

SPIEN = 1 and MSTM = 0

P0.5

Special

SCLK—SPI Clock Output (Master Mode)

SPIEN = 1 and MSTM = 1

P0.6

Alternate

External Interrupt 6

(EIE0.6) EX6 = 1

P0.6

Alternate

MOSI—SPI Slave Input (Slave Mode)

SPIEN = 1 and MSTM = 0

P0.6

Special

MOSI—SPI Master Output (Master Mode)

SPIEN = 1 and MSTM = 1

P0.7

Alternate

External Interrupt 7

(EIE0.7) EX7 = 1

P0.7

Special

MISO—SPI Slave Output (Slave Mode)

SPIEN = 1 and MSTM = 0

P0.7

Alternate

MISO—SPI Master Input (Master Mode)

SPIEN = 1 and MSTM = 1

P1.0

Alternate

External Interrupt 8

(EIE1.0) EX8 = 1

P1.0

Special

Serial Port Data (Mode 0)

Mode 0: SBUF is written or REN is set to 1

(until serial transmission completes)

P1.0

Alternate

Serial Port Receive (Modes 1/2/3)

Modes 1/2/3: REN = 1

P1.0

Special

SCL—I

2

C Clock Line

I2CEN=1 (overrides serial port Rx)

P1.1

Alternate

External Interrupt 9

(EIE1.1) EX9 = 1

Maxim Integrated