8 reset conditions, 8 reset conditions -8, Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

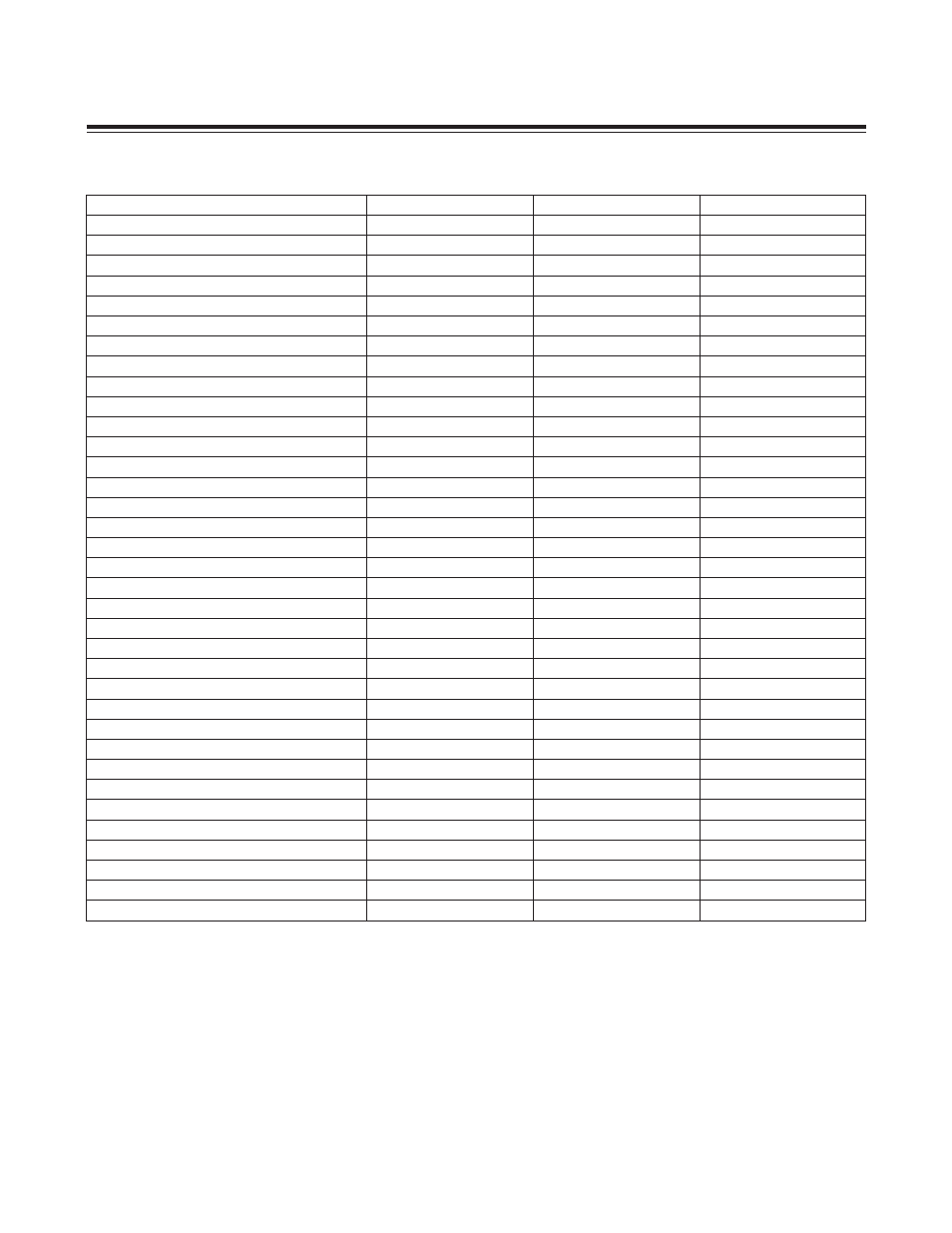

Page 17: Table 2-2. interrupt sources and control bits

MAXQ Family User’s Guide:

MAXQ8913 Supplement

2-8

2.8 Reset Conditions

There are four possible reset sources for the MAXQ8913. While in the reset state, the enabled system clock oscillator

continues running, but no code execution occurs. Once the reset condition has been removed or has completed, code

execution resumes at address 8000h for all reset types.

Table 2-2. Interrupt Sources and Control Bits

INTERRUPT

MODULE ENABLE BIT

LOCAL ENABLE BIT

INTERRUPT FLAG

Watchdog Interrupt

IMS (IMR.7)

EWDI (WDCN.6)

WDIF (WDCN.3)

External Interrupt 0 (P0.0)

IM0 (IMR.0)

EX0 (EIE0.0)

IE0 (EIF0.0)

External Interrupt 1 (P0.1)

IM0 (IMR.0)

EX1 (EIE0.1)

IE1 (EIF0.1)

External Interrupt 2 (P0.2)

IM0 (IMR.0)

EX2 (EIE0.2)

IE2 (EIF0.2)

External Interrupt 3 (P0.3)

IM0 (IMR.0)

EX3 (EIE0.3)

IE3 (EIF0.3)

External Interrupt 4 (P0.4)

IM0 (IMR.0)

EX4 (EIE0.4)

IE4 (EIF0.4)

External Interrupt 5 (P0.5)

IM0 (IMR.0)

EX5 (EIE0.5)

IE5 (EIF0.5)

External Interrupt 6 (P0.6)

IM0 (IMR.0)

EX6 (EIE0.6)

IE6 (EIF0.6)

External Interrupt 7 (P0.7)

IM0 (IMR.0)

EX7 (EIE0.7)

IE7 (EIF0.7)

External Interrupt 8 (P1.0)

IM0 (IMR.0)

EX8 (EIE1.0)

IE8 (EIF1.0)

External Interrupt 9 (P1.1)

IM0 (IMR.0)

EX9 (EIE1.1)

IE9 (EIF1.1)

External Interrupt 10 (P1.2)

IM0 (IMR.0)

EX10 (EIE1.2)

IE10 (EIF1.2)

External Interrupt 11 (P1.3)

IM0 (IMR.0)

EX11 (EIE1.3)

IE11 (EIF1.3)

Supply Voltage Monitor Interrupt

IM0 (IMR.0)

SVMIE (SVM.2)

SVMI (SVM.3)

Serial Port Receive

IM1 (IMR.1)

ESI (SMD.2)

RI (SCON.0)

Serial Port Transmit

IM1 (IMR.1)

ESI (SMD.2)

TI (SCON.1)

SPI Mode Fault Interrupt

IM1 (IMR.1)

ESPII (SPICF.7)

MODF (SPICN.3)

SPI Write Collision Interrupt

IM1 (IMR.1)

ESPII (SPICF.7)

WCOL (SPICN.4)

SPI Receive Overrun Interrupt

IM1 (IMR.1)

ESPII (SPICF.7)

ROVR (SPICN.5)

SPI Transfer Complete Interrupt

IM1 (IMR.1)

ESPII (SPICF.7)

SPIC (SPICN.6)

I

2

C START Condition Interrupt

IM1 (IMR.1)

I2CSRI (I2CST.0)

I2CSRIE (I2CIE.0)

I

2

C Transmit Complete Interrupt

IM1 (IMR.1)

I2CTXI (I2CST.1)

I2CTXIE (I2CIE.1)

I

2

C Receive Ready Interrupt

IM1 (IMR.1)

I2CRXI (I2CST.2)

I2CRXIE (I2CIE.2)

I

2

C Clock Stretch Interrupt

IM1 (IMR.1)

I2CSTRI (I2CST.3)

I2CSTRIE (I2CIE.3)

I

2

C Timeout Interrupt

IM1 (IMR.1)

I2CTOI (I2CST.4)

I2CTOIE (I2CIE.4)

I

2

C Slave Address Match Interrupt

IM1 (IMR.1)

I2CAMI (I2CST.5)

I2CAMIE (I2CIE.5)

I

2

C Arbitration Loss Interrupt

IM1 (IMR.1)

I2CALI (I2CST.6)

I2CALIE (I2CIE.6)

I

2

C NACK Interrupt

IM1 (IMR.1)

I2CNACKI (I2CST.7)

I2CNACKIE (I2CIE.7)

I

2

C General Call Address Interrupt

IM1 (IMR.1)

I2CGCI (I2CST.8)

I2CGCIE (I2CIE.8)

I

2

C Receiver Overrun Interrupt

IM1 (IMR.1)

I2CROI (I2CST.9)

I2CROIE (I2CIE.9)

I

2

C STOP Condition Interrupt

IM1 (IMR.1)

I2CSPI (I2CST.11)

I2CSPIE (I2CIE.11)

Type B Timer—External Trigger

IM2 (IMR.2)

EXFB (TBCN.6)

ETB (TBCN.1)

Type B Timer—Overflow

IM2 (IMR.2)

TFB (TBCN.7)

ETB (TBCN.1)

ADC Data Available Interrupt

IM3 (IMR.3)

ADDAIE (ADCN.5)

ADDAI (ADST.5)

Amplifier Interrupt

IM3 (IMR.3)

AMPIE (AMPCN.4)

AMPIF (AMPCN.5)

Maxim Integrated