Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 77

MAXQ Family User’s Guide:

MAXQ8913 Supplement

21-2

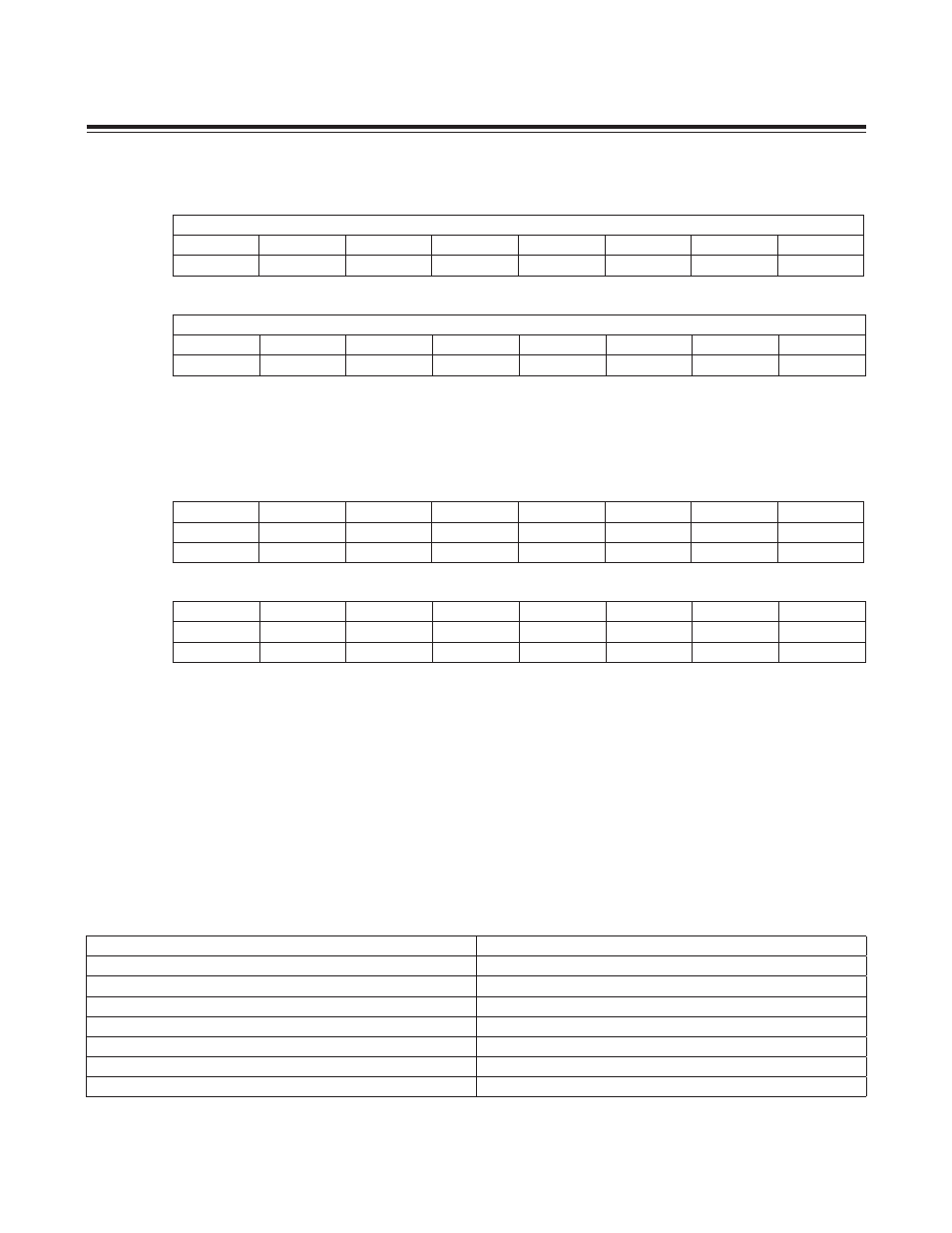

21.1.2 Timer B Timer/Counter Compare Register (TBC, M2[0Bh])

Bits 15:0: Timer B Compare Register. This register is used for comparison vs. the TBV value when Timer B is oper-

ated in compare mode.

21.1.3 Timer B Timer/Counter Control Register (TBCN, M2[06h])

Bit 15: Counter/Timer Select (C/TB). This bit determines whether Timer B functions as a timer or counter. Setting this

bit to 1 causes Timer B to count negative transitions on the TB0A pin. Clearing this bit to 0 causes Timer B to function

as a timer. The speed of Timer B is determined by the TBPS[2:0] bits of TBCN.

Bits 14:13: Reserved. Read returns zero.

Bits 12:11: TB0B Pin Output Reset/Set Mode Bits (TBCS, TBCR). These mode bits define whether the PWM mode

output function is enabled on the TB0B pin, the initial output starting state, and what compare mode output function is

in effect. Note that the TB0B pin still has certain input functionality when the PWM output function is enabled.

Bits 10:8: Timer B Clock Prescaler Bits (TBPS[2:0]). These bits select the clock prescaler applied to the system

clock input to Timer B. The TBPS[2:0] bits should be configured by the user when the timer is stopped (TRB = 0).

While hardware does not prevent changing the TBPS[2:0] bits when the timer is running, the resultant behavior is

indeterministic.

Timer B Clock = System Clock/2

(2 x TBPS[2:0])

Bit #

15

14

13

12

11

10

9

8

Name

TBC

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

TBC

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

15

14

13

12

11

10

9

8

Name

C/TB

—

—

TBCS

TBCR

TBPS2

TBPS1

TBPS0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

TFB

EXFB

TBOE

DCEN

EXENB

TRB

ETB

CP/RLB

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

TBPS[2:0]

TIMER B INPUT CLOCK

000

Sysclk/1

001

Sysclk/4

010

Sysclk/16

011

Sysclk/64

100

Sysclk/256

101

Sysclk/1024

11x

Sysclk/1

Maxim Integrated