5 i2c clock control register (i2cck, m1[0ch]), 6 i2c timeout register (i2cto, m1[0dh]), C clock control register (i2cck, m1[0ch]) -6 – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 92: C timeout register (i2cto, m1[0dh]) -6, Maxq family user’s guide: maxq8913 supplement, C clock control register (i2cck, m1[0ch]), C timeout register (i2cto, m1[0dh])

MAXQ Family User’s Guide:

MAXQ8913 Supplement

22-6

22.1.5 I

2

C Clock Control Register (I2CCK, M1[0Ch])

Bits 15:8: I

2

C Clock High (I2CCKH[7:0]). These bits define the I

2

C SCL high period in number of system clocks, with

bit 7 as the most significant bit. The duration of SCL high time is calculated using the following equation:

I

2

C High Time Period = System Clock x (I2CCKH[7:0] + 1)

When operating in master mode, I2CCKH must be set to a minimum value of 2 to ensure proper operation. Any value

less than 2 is set to 2.

Bits 7:0: I

2

C Clock Low (I2CCKL[7:0]). These bits define the I

2

C SCL low period in number of system clocks, with bit

7 as the most significant bit. The duration of SCL low time is calculated using the following equation:

I

2

C Low Time Period = System Clock x (I2CCKL[7:0] + 1)

When operating in master mode, I2CCKL must be set to a minimum value of 4 to ensure proper operation. Any value

less than 4 is set to 4.

22.1.6 I

2

C Timeout Register (I2CTO, M1[0Dh])

Bits 7:0: I

2

C Timeout Register. This register is used only in master mode. This register determines the number of the

I

2

C bit period (SCL high + SCL low) the I

2

C master waits for SCL to go high. The timeout timer resets to 0 and starts to

count after the I2CSTART bit is set, or every time SCL goes low. When cleared to 00h, the timeout function is disabled

and the I

2

C waits for SCL to go high indefinitely during a transmission. When set to any other values, the I

2

C waits until

the timeout expires and sets the I2CTOI flag.

I

2

C Timeout = I

2

C Bit Rate x (I2CTO[7:0] + 1)

Note that these bits have no effect when the I

2

C module is operating in slave mode (I2CMST = 0). When operating in

slave mode, SCL is controlled by an external master.

Note 1: Write to this register is ignored when I2CBUSY = 0.

Note 2: This register has no function in slave mode.

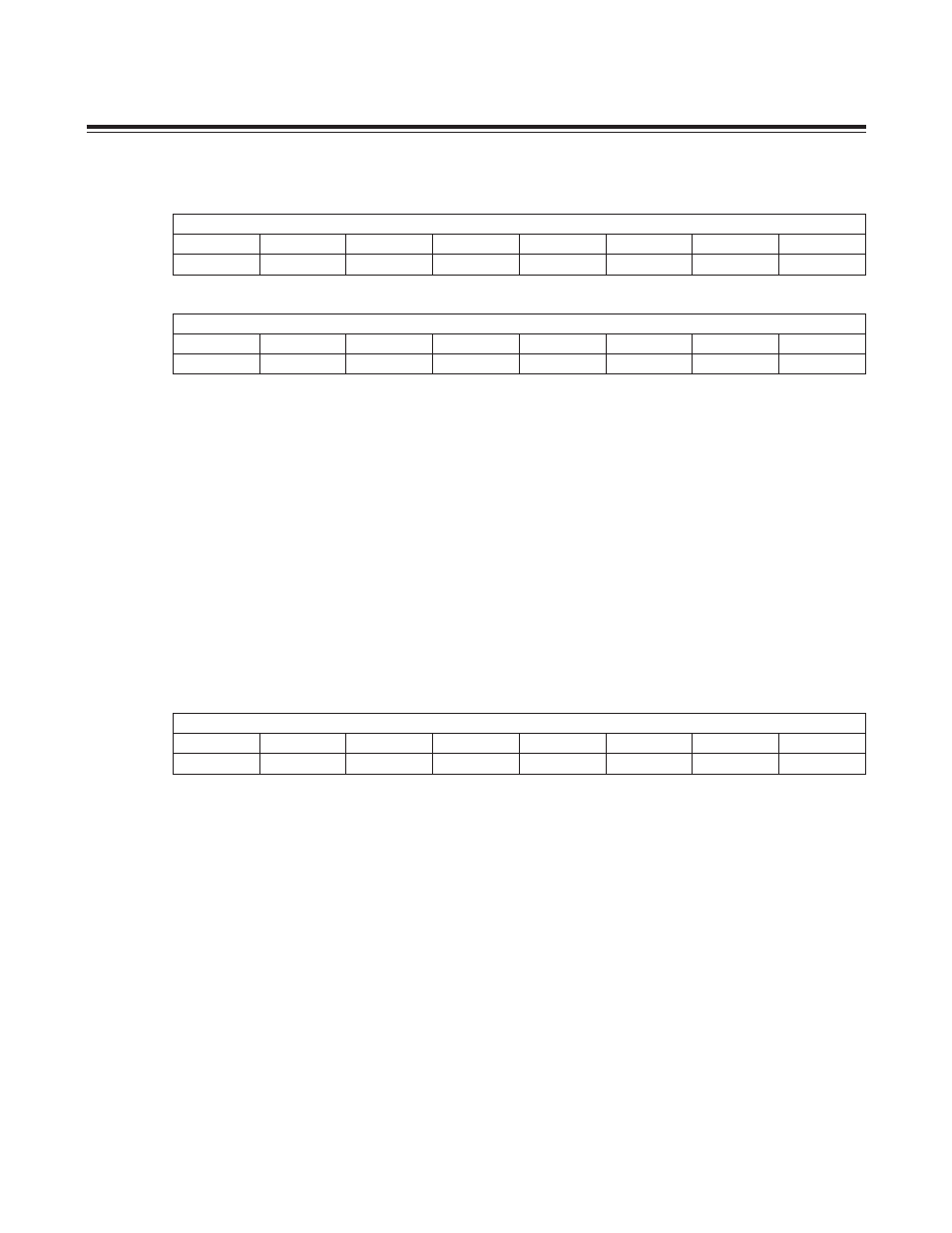

Bit #

7

6

5

4

3

2

1

0

Name

I2CTO

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

15

14

13

12

11

10

9

8

Name

I2CCKH

Reset

0

0

0

0

0

0

1

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

I2CCKL

Reset

0

0

0

0

0

1

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Maxim Integrated