4 i2c control register (i2ccn, m1[04h]), C control register (i2ccn, m1[04h]) -4, Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 90: C control register (i2ccn, m1[04h])

MAXQ Family User’s Guide:

MAXQ8913 Supplement

22-4

Bit 9: I

2

C Receiver Overrun Interrupt Enable (I2CROIE). Setting this bit to 1 causes an interrupt to the CPU when a

receiver overrun condition is detected (I2ROI = 1). Clearing this bit to 0 disables receiver overrun detection interrupt

from generating.

Bit 8: I

2

C General Call Interrupt Enable (I2CGCIE). Setting this bit to 1 generates an I2CGCI (general call interrupt)

to the CPU when general call is enabled (I2CGCEN = 1). Clearing this bit to 0 disables general call interrupt from

generating.

Bit 7: I

2

C NACK Interrupt Enable (I2CNACKIE). Setting this bit to 1 causes an interrupt to the CPU when a NACK is

detected (I2CNACKI = 1). Clearing this bit to 0 disables NACK detection interrupt from generating.

Bit 6: I

2

C Arbitration Loss Interrupt Enable (I2CALIE). Setting this bit to 1 causes an interrupt to the CPU when the

I

2

C master loses in an arbitration (I2CALI = 1). Clearing this bit to 0 disables arbitration loss interrupt from generating.

Bit 5: I

2

C Slave Address Match Interrupt Enable (I2CAMIE). Setting this bit to 1 causes an interrupt to the CPU

when the I

2

C controller detects an address that matches the I2CSLA value (I2CAMI = 1). Clearing this bit to 0 disables

address match interrupt from generating.

Bit 4: I

2

C Timeout Interrupt Enable (I2CTOIE). Setting this bit to 1 causes an interrupt to the CPU when a timeout

condition is detected (I2CTOI = 1). Clearing this bit to 0 disables timeout interrupt from generating.

Bit 3: I

2

C Clock Stretch Interrupt Enable (I2CSTRIE). Setting this bit to 1 generates an interrupt to the CPU when the

clock stretch interrupt flag is set (I2CSTRI = 1). Clearing this bit disables the clock stretch interrupt from generating.

Bit 2: I

2

C Receive Ready Interrupt Enable (I2CRXIE). Setting this bit to 1 causes an interrupt to the CPU when the

receive interrupt flag is set (I2CRXI = 1). Clearing this bit to 0 disables the receive interrupt from generating.

Bit 1: I

2

C Transmit Complete Interrupt Enable (I2CTXIE). Setting this bit to 1 causes an interrupt to the CPU when

the transmit interrupt flag is set (I2CTXI = 1). Clearing this bit to 0 disables the transmit interrupt from generating.

Bit 0: I

2

C START Interrupt Enable (I2CSRIE). Setting this bit to 1 causes an interrupt to the CPU when a START condi-

tion is detected (I2CSRI = 1). Clearing this bit to 0 disables the START detection interrupt from generating.

22.1.4 I

2

C Control Register (I2CCN, M1[04h])

Bit 15: I

2

C Reset (I2CRST). Setting this bit to 1 aborts the current transaction and resets the I

2

C controller. This bit is

set to 1 by software and is only cleared to 0 by hardware after the reset or when I2CEN = 0.

Bits 14:10: Reserved. Read returns 0.

Bit 9: I

2

C Clock Stretch Enable (I2CSTREN). Setting this bit to 1 stretches the clock (holds SCL low) at the end of the

clock cycle specified in I2CSTRS. Clearing this bit disables clock stretching.

Note 1: I2CSTART and I2CSTOP are mutually exclusive and reset to 0 when I2CMST = 0 or I2CEN = 0.

Note 2: I2CRST is reset to 0 when I2CEN = 0.

Note 3: Writes to I2CMST, I2CMODE, and I2CEN are ignored when I2CBUSY = 1.

Note 4: If I2CRST = 1, I2CEN can be written when I2CBUSY = 1.

Note 5: Write to I2CACK is ignored if I2RST = 1.

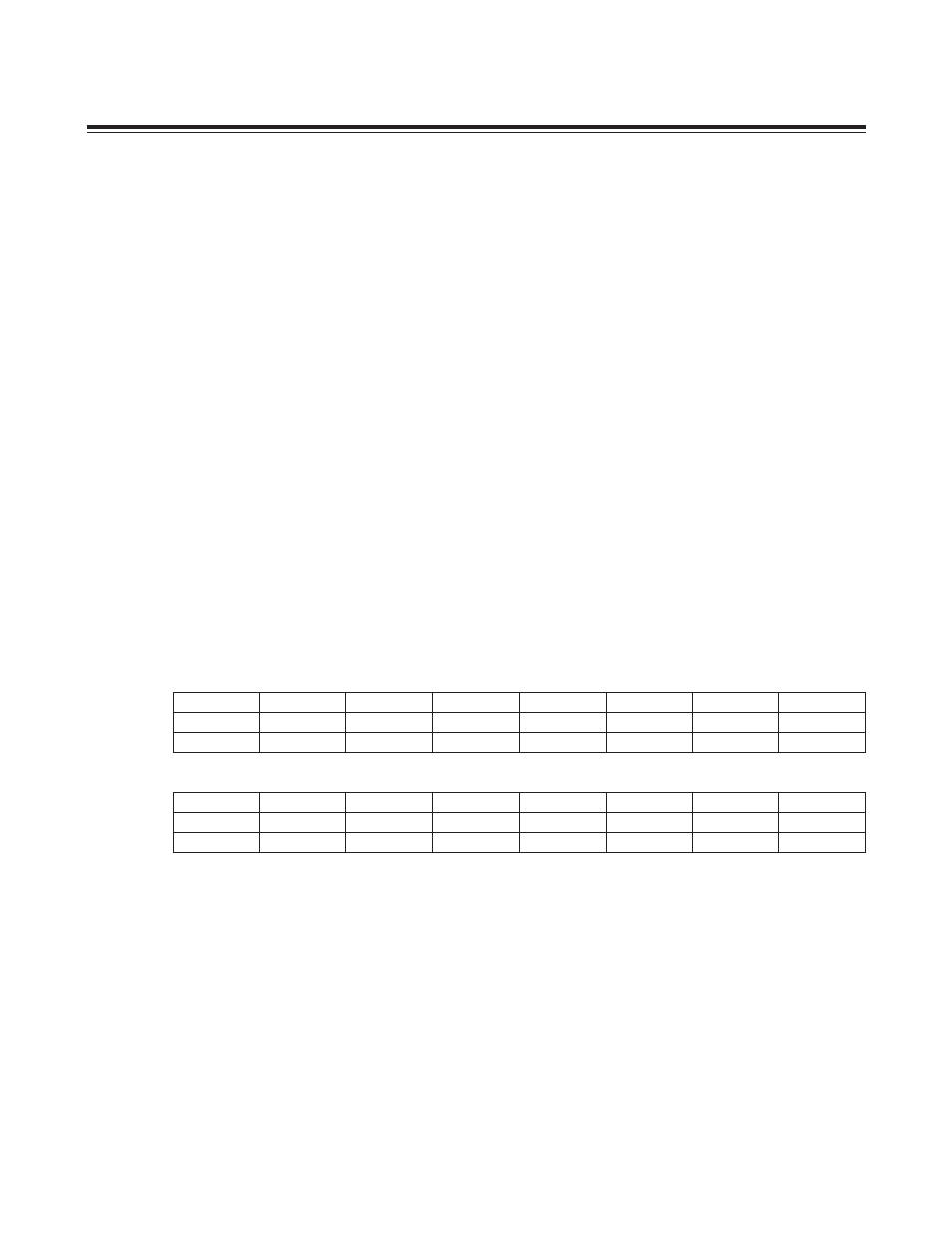

Bit #

15

14

13

12

11

10

9

8

Name

I2CRST

—

—

—

—

—

I2CSTREN

I2CGCEN

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

I2CSTOP

I2CSTART

I2CACK

I2CSTRS

I2CEA

I2CMODE

I2CMST

I2CEN

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Maxim Integrated