Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 81

MAXQ Family User’s Guide:

MAXQ8913 Supplement

21-6

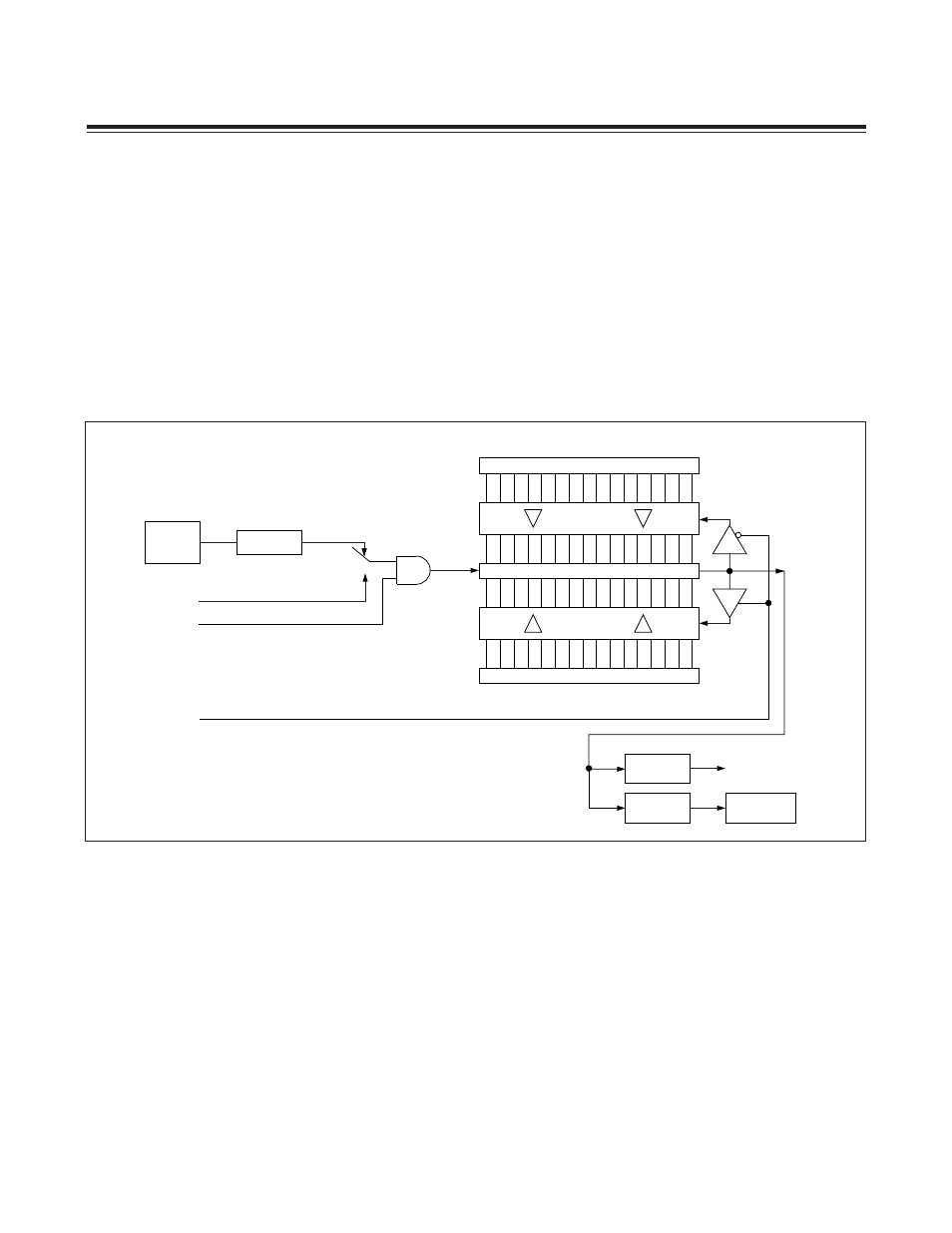

21.2.3 Timer B 16-Bit Up/Down Count with Autoreload Mode

The 16-bit up/down-count autoreload mode is enabled by clearing the capture/reload bit CP/RLB of the control register

(TBCN.0) to 0 and setting the down-count enable bit, DCEN (TBCN.4), to 1. This mode is illustrated in Figure 21-3.

When DCEN is set to 1, Timer B counts up from 0000h or down from the value contained in the TBR register as con-

trolled by the state of the TB0B pin. When the TB0B pin is 1, the timer counts up, and counts down when the pin is 0.

When DCEN is 0, Timer B can only count up.

When counting up and a match occurs between the value in the TBV register and value in the TBR register, the value

of 0000h is loaded into the TBV register. When counting down and the value in the TBV register reaches 0000h, the

value in the TBR register is loaded into the TBV register and downward counting continues.

Note that in this mode of operation, the overflow/underflow output of the timer is provided to an edge-detection circuit

as well as to the TBF bit of the control register (TBCN.7). This edge-detection circuit toggles the EXFB bit (TBCN.6) on

every overflow or underflow. Therefore, the EXFB bit behaves as a 17th bit of the counter, and can be used as such.

Figure 21-3. Timer B 16-Bit Up/Down Count with Autoreload Mode Block Diagram

TIMER B INTERRUPT

15

0

15

0

(DOWN-COUNTING RELOAD VALUE)

(UP-COUNTING RELOAD VALUE)

COUNT DIRECTION (1 = UP, 0 = DOWN)

TB0B PIN

TBR

TBV

0000h

0

1

TB0A PIN

TRB = TBCN.2

SYSTEM

CLOCK

C/TB = TBCN.15

TFB = TBCN.7

EXFB = TBCN.6

RISE/FALL

EDGE

/CLK

2

(2 x TBPS[2:0])

TBPS[2:0] = TBCN[10:8]

Maxim Integrated