7 interrupts, 7 interrupts -7, Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 16

MAXQ Family User’s Guide:

MAXQ8913 Supplement

2-7

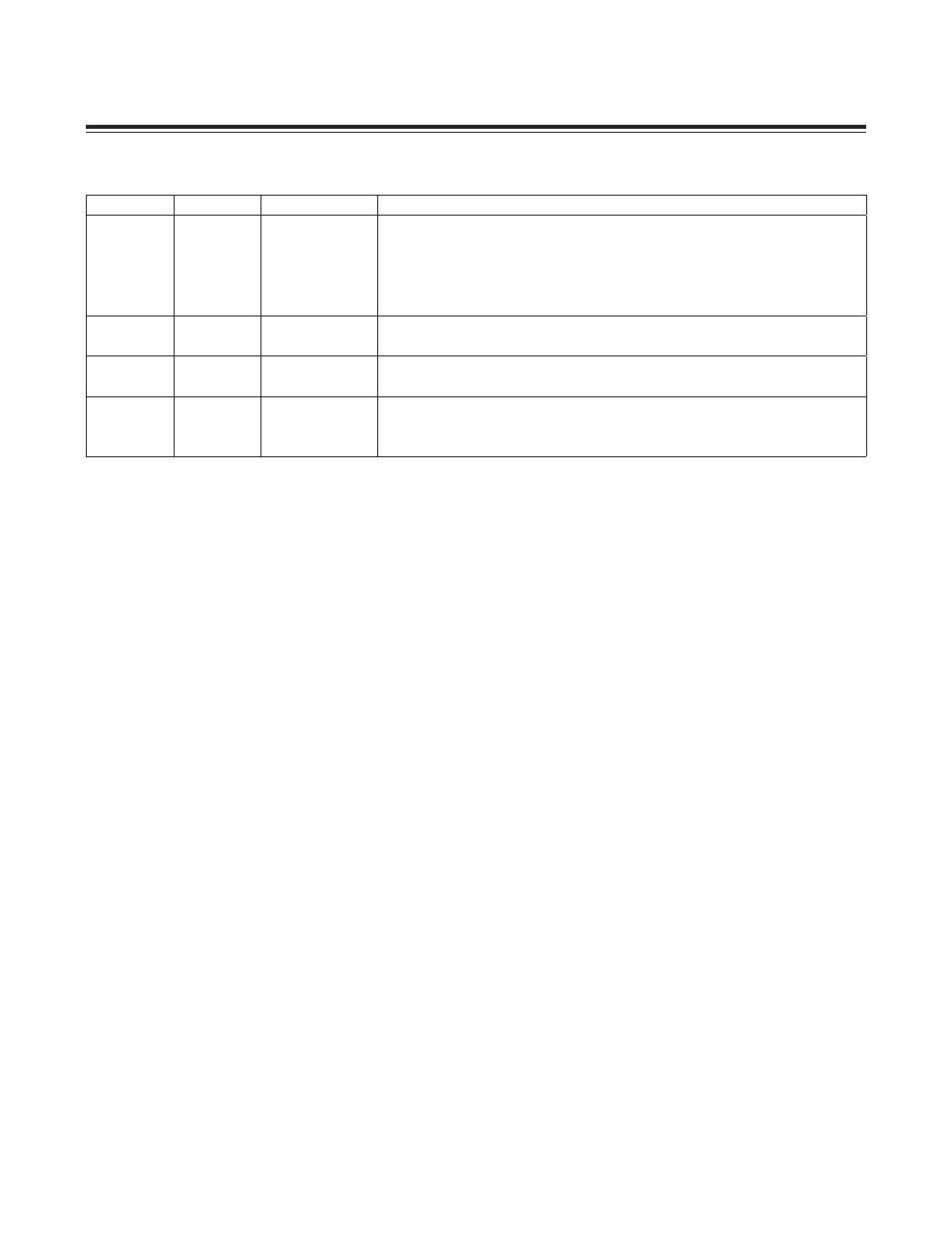

Table 2-1. System Clock Generation and Control Registers

Because the RGSL bit is cleared by power-on reset only, if this bit is set before entering stop mode, the ring oscillator

is still used as the system clock source when stop mode is exited. In this case, a 10-ring oscillator cycle warmup delay

is required when exiting stop mode before execution resumes using the ring oscillator as the system clock source.

When the system clock source is switched back from the ring oscillator to the high-frequency oscillator by clearing

RGSL to 0, the ring oscillator is still used as the system clock source until the warmup period has completed for the

high-frequency oscillator. This is reflected by the value of the RGMD bit, which remains at 1 until the warmup for the

high-frequency oscillator has completed and the clock switches over, at which point RGMD switches to 0.

2.7 Interrupts

In general, interrupt handling on the MAXQ8913 operates as described in the MAXQ Family User’s Guide. All interrupt

sources have the same priority, and all interrupts cause program execution to branch to the location specified by the

Interrupt Vector (IV) register, which defaults to 0000h.

Table 2-2 lists all possible interrupt sources for the MAXQ8913, along with their corresponding module interrupt enable

bits, local interrupt enable bits, and interrupt flags.

• Each module interrupt enable bit, when cleared to 0, blocks interrupts originating in that module from being acknowl-

edged. When the module interrupt enable bit is set to 1, interrupts from that module are acknowledged (unless all

interrupts have been disabled globally).

• Each local interrupt enable bit, when cleared to 0, disables the corresponding interrupt. When the local interrupt-

enable bit is set to 1, the interrupt is triggered whenever its interrupt flag is set to 1 by hardware or by software.

• Each interrupt flag bit, when set to 1, causes its corresponding interrupt to trigger. Interrupt flag bits are typically set

by hardware and must be cleared by software (generally in the interrupt handler routine).

Note that for an interrupt to fire, the following five conditions must exist:

• Interrupts must be enabled globally by setting IGE (IC.0) to 1.

• The module interrupt enable bit for the interrupt source’s module must be set to 1.

• The local interrupt enable bit for the specific interrupt source must be set to 1.

• The interrupt flag for the interrupt source must be set to 1. Typically, this is done by hardware when the condition

that requires interrupt service occurs.

• The interrupt-in-service (INS) bit must be cleared to 0. This bit is set automatically upon vectoring to the interrupt

handler (IV) address and cleared automatically upon exit (RETI/POPI), so the only reason to clear this bit manually

(inside the interrupt handler routine) is to allow nested interrupt handling.

REGISTER

ADDRESS

BIT(S)

FUNCTION

CKCN

M8[0Eh]

[2:0]—PMME,

CD[1:0]

000: System clock = high-frequency clock divided by 1.

001: System clock = high-frequency clock divided by 2.

010: System clock = high-frequency clock divided by 4.

011: System clock = high-frequency clock divided by 8.

1xx: System clock = high-frequency clock/256.

CKCN

M8[0Eh]

5—RGMD

0: System clock is being provided by an external source.

1: System clock is being provided by the ring oscillator.

CKCN

M8[0Eh]

6—RGSL

0: Selects an external source for system clock generation.

1: Selects the ring oscillator for system clock generation.

PWCN

M0[0Ch]

0—HFXD

0: High-frequency oscillator operates normally (default).

1: Disables the high-frequency oscillator, allowing an external clock to be

provided at HFXIN.

Maxim Integrated