3 analog-to-digital converter code examples, 1 adc example 1: single conversion, 2 adc example 2: continuous conversion – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 71: 3 analog-to-digital converter code examples -9, Maxq family user’s guide: maxq8913 supplement

MAXQ Family User’s Guide:

MAXQ8913 Supplement

19-9

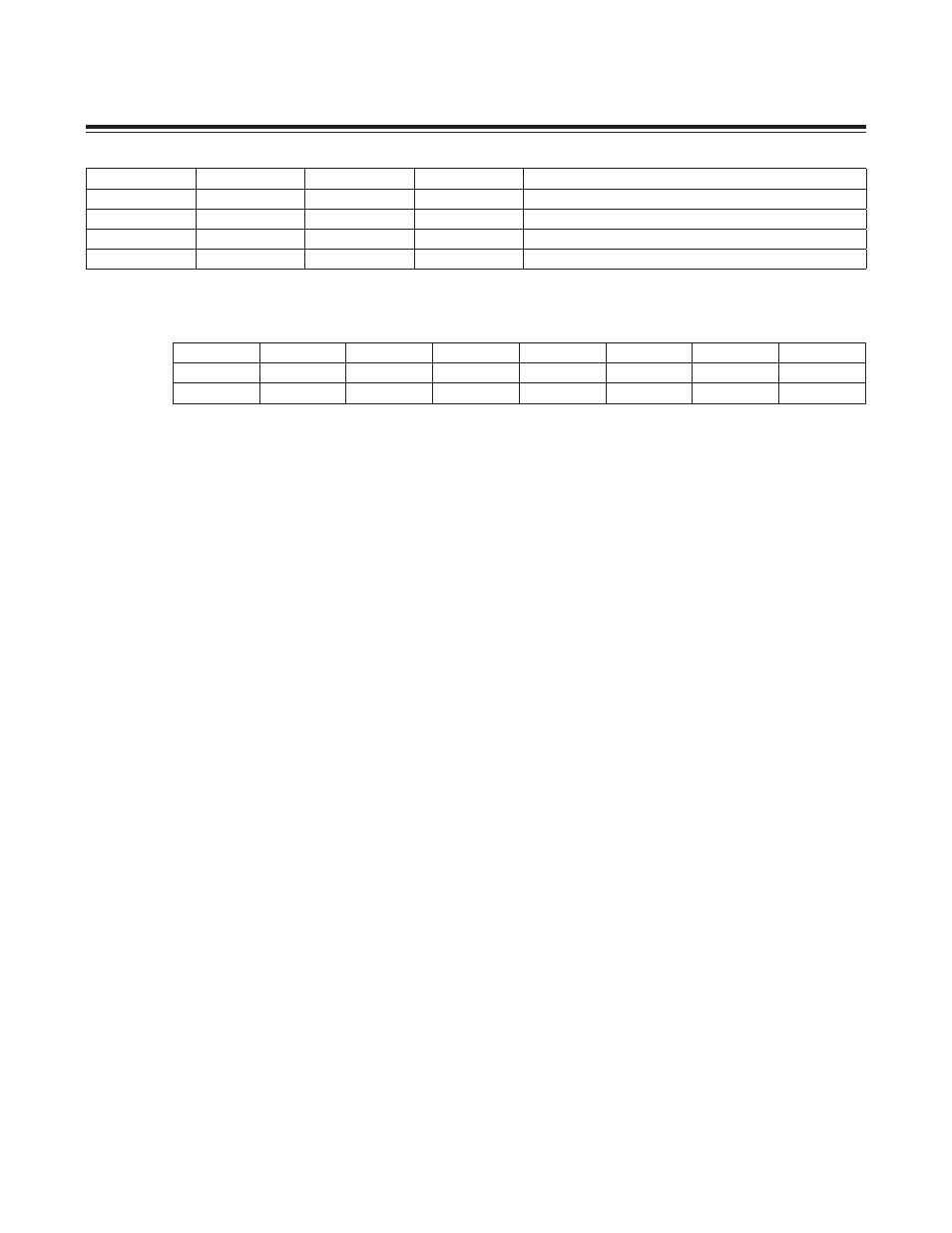

19.2.7 Temperature Sensor Enable Register (TEMPEN, M3[0Ch])

Bits 7:1: Reserved

Bit 0: Temperature Sensor Enable (TSEN). This bit enables/disables the on-board temperature sensor whose value

can be read through ADC channel 6 (single-ended mode only).

0 = Temperature sensor is disabled (default value).

1 = Temperature sensor is enabled.

19.3 Analog-to-Digital Converter Code Examples

19.3.1 ADC Example 1: Single Conversion

move ADCN, #0300h ; Set ADC clock to sysclk/8 (78ksps at 10MHz)

move ADST, #0010h ; Points ADDATA to config register 0

move ADDATA, #06h

; Single-ended conversion on channel AN6, AVDD ref

move ADST.6, #1

; Start conversion

waitConvert:

move C, ADST.6

jump C, waitConvert

; Conversion has completed when ADST.6 clears to 0

move ADST, #0000h ; Points ADDATA to data register 0

move Acc, ADDATA ; Get conversion result

19.3.2 ADC Example 2: Continuous Conversion

move ADCN, #0F00h ; Set ADC clock to sysclk/8 (78ksps at 10MHz),

; also set Data Available interrupt to trigger

; following every 16 samples

move ADCN.6, #1

; Enable continuous conversion mode

move ADST, #0010h ; Points ADDATA to config register 0

move ADDATA, #06h

; ACFG[0]: Single-ended conversion on AN6, AVDD ref

move ADDATA, #07h

; ACFG[1]: Single-ended conversion on AN7, AVDD ref

move ADADDR, #0001h

; Sequence runs from ACFG[0] to ACFG[1] inclusive

move ADST.6, #1

; Start conversion (continuous)

ADDIFF

ADCH2

ADCH1

ADCH0

ADC CONVERSION TYPE

1

X

0

0

Differential conversion: (AIN0, AIN1)

1

X

0

1

Differential conversion: (AIN2, AIN3)

1

X

1

0

Differential conversion: (AIN4, AIN5)

1

X

1

1

Reserved

Bit #

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

—

TSEN

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

rw

Maxim Integrated