3 system control register (sc, m8[08h]), 4 interrupt identification register (iir, m8[0bh]), Maxq family user’s guide: maxq8913 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ8913 Supplement User Manual

Page 26

MAXQ Family User’s Guide:

MAXQ8913 Supplement

4-4

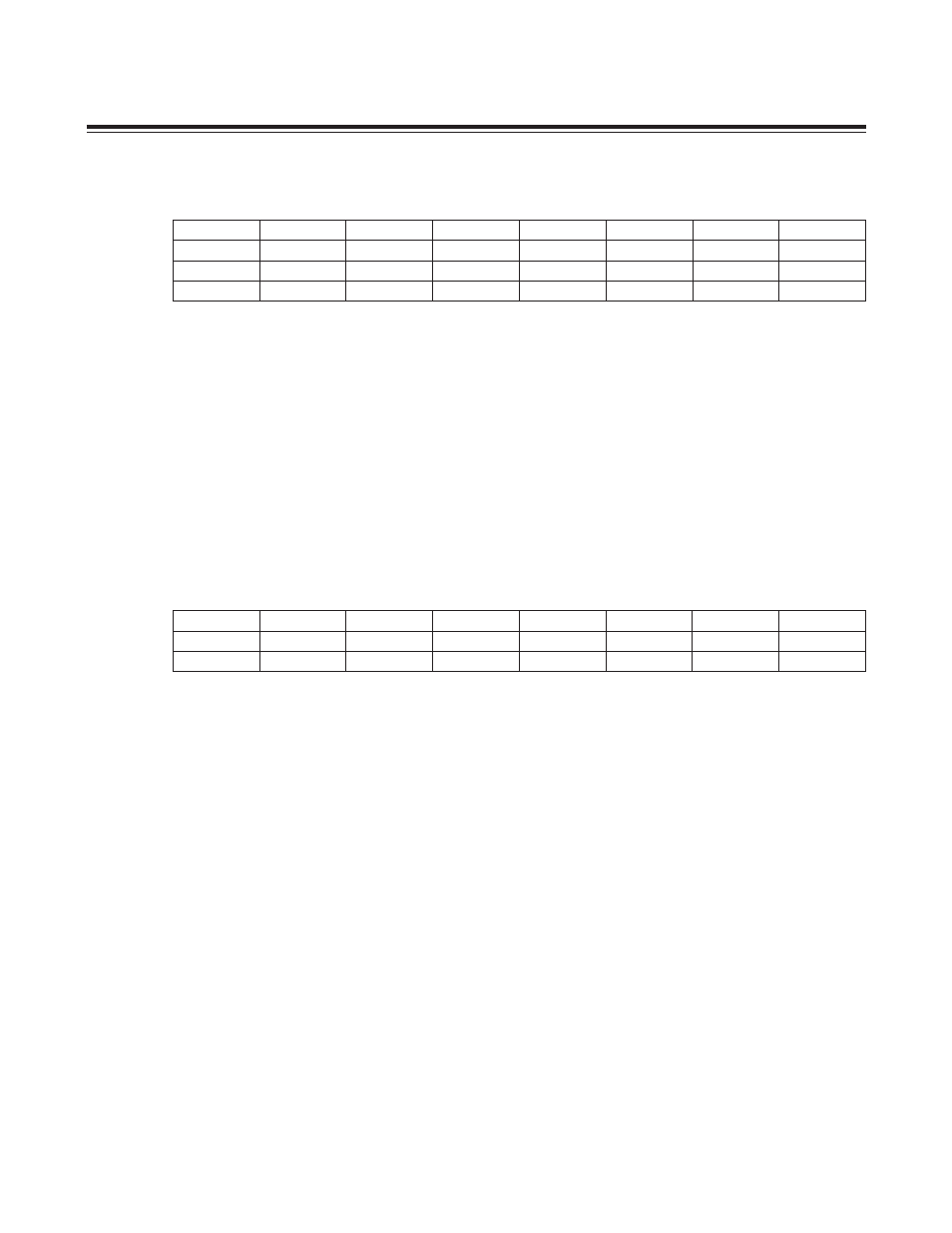

4.1.3 System Control Register (SC, M8[08h])

Bit 7: Test Access (Debug) Port Enable (TAP)

0 = Debug port functions are disabled, and P0.0 to P0.3 can be used as general-purpose I/O pins.

1 = Port pins P0.0 to P0.3 are enabled to act as debug port (JTAG) inputs and outputs.

Bits 6:5, 3:2, 0: Reserved

Bit 4: Code Data Access (CDA0). Setting this bit to 0 or 1 enables access to either the low or high page of program

memory in data space when accessing data in byte mode, as shown in Figure 2-3 and Figure 2-4. When accessing

data space in word mode, the setting of this bit has no effect.

Bit 1: Password Lock (PWL). This bit defaults to 1 on power-on reset only. When this bit is 1, it requires a 32-byte

password to be matched with the password in the program space (words 10h to 1Fh) before allowing access to the

ROM loader’s utilities for read/write of program memory and debug functions. Clearing this bit to 0 disables the pass-

word protection to the ROM loader.

4.1.4 Interrupt Identification Register (IIR, M8[0Bh])

The first three bits in this register indicate interrupts pending in modules 0 to 3, one bit per module. The eighth bit, IIS,

indicates a pending system interrupt (from the watchdog timer or other system function). The interrupt pending flags

are set only for enabled interrupt sources waiting for service. The interrupt pending flag is cleared when the pending

interrupt source(s) within that module are disabled or when the interrupt flag(s) are cleared by software.

Bit 7: Interrupt Pending Flag for System Modules (IIS)

Bits 6:4: Reserved

Bit 3: Interrupt Pending Flag for Module 3 (II3)

Bit 2: Interrupt Pending Flag for Module 2 (II2)

Bit 1: Interrupt Pending Flag for Module 1 (II1)

Bit 0: Interrupt Pending Flag for Module 0 (II0)

Bit #

7

6

5

4

3

2

1

0

Name

TAP

—

—

CDA0

—

—

PWL

—

Reset

1

0

0

0

0

0

Unchanged

0

POR

1

0

0

0

0

0

1

0

Access

rw

r

r

r

r

r

rw

r

Bit #

7

6

5

4

3

2

1

0

Name

IIS

—

—

—

II3

II2

II1

II0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Maxim Integrated