Interrupt, D in section “interrupt, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 66

66

AT8xC51SND1C

4109E–8051–06/03

Interrupt

Description

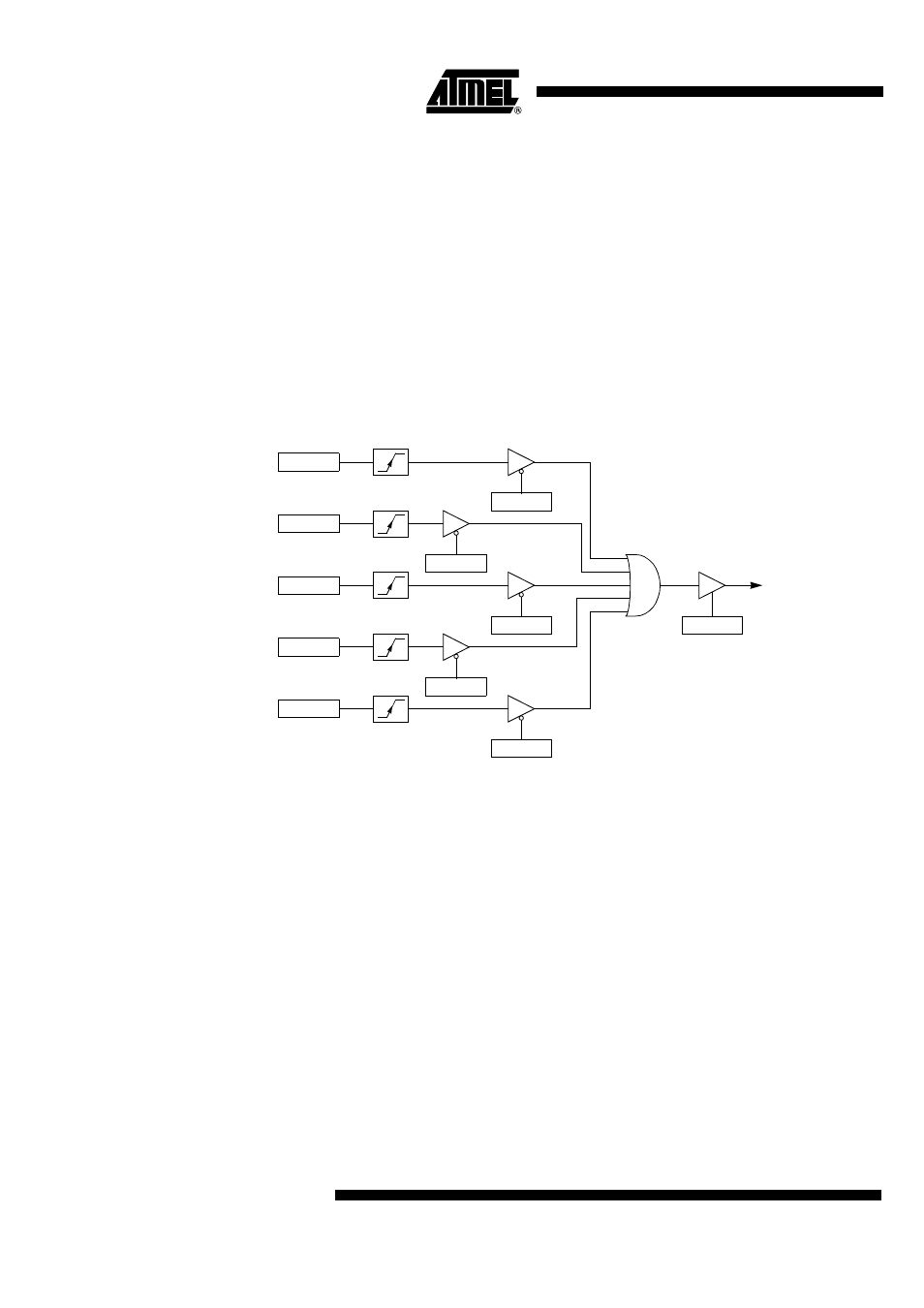

As shown in Figure 46, the MP3 decoder implements five interrupt sources reported in

ERRCRC, ERRSYN, ERRLAY, MPREQ, and MPANC flags in MP3STA register.

All these sources are maskable separately using MSKCRC, MSKSYN, MSKLAY,

MSKREQ, and MSKANC mask bits respectively in MP3CON register.

The MP3 interrupt is enabled by setting EMP3 bit in IEN0 register. This assumes inter-

rupts are globally enabled by setting EA bit in IEN0 register.

All interrupt flags but MPREQ and MPANC are cleared when reading MP3STA register.

The MPREQ flag is cleared by hardware when no more data is requested (see

Figure 43) and MPANC flag is cleared by hardware when the ancillary buffer becomes

empty.

Figure 46. MP3 Decoder Interrupt System

Management

Reading the MP3STA register automatically clears the interrupt flags (acknowledgment)

except the MPREQ and MPANC flags. This implies that register content must be saved

and tested, interrupt flag by interrupt flag to be sure not to forget any interrupts.

MP3 Decoder

Interrupt Request

MPANC

MP3STA.7

MSKLAY

MP3CON.2

EMP3

IEN0.5

MSKANC

MP3CON.4

MSKREQ

MP3CON.3

ERRSYN

MP3STA.4

MSKCRC

MP3CON.0

MSKSYN

MP3CON.1

MPREQ

MP3STA.6

ERRCRC

MP3STA.3

ERRLAY

MP3STA.5