Interrupt, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 55

55

AT8xC51SND1C

4109E–8051–06/03

Mode 0 (13-bit Timer)

Mode 0 configures Timer 1 as a 13-bit Timer, which is set up as an 8-bit Timer (TH1 reg-

ister) with a modulo-32 prescaler implemented with the lower 5 bits of the TL1 register

(see Figure 29). The upper 3 bits of TL1 register are ignored. Prescaler overflow incre-

ments TH1 register.

Mode 1 (16-bit Timer)

Mode 1 configures Timer 1 as a 16-bit Timer with TH1 and TL1 registers connected in

cascade (see Figure 31). The selected input increments TL1 register.

Mode 2 (8-bit Timer with Auto-

Reload)

Mode 2 configures Timer 1 as an 8-bit Timer (TL1 register) with automatic reload from

TH1 register on overflow (see Figure 33). TL1 overflow sets TF1 flag in TCON register

and reloads TL1 with the contents of TH1, which is preset by software. The reload

leaves TH1 unchanged.

Mode 3 (Halt)

Placing Timer 1 in mode 3 causes it to halt and hold its count. This can be used to halt

Timer 1 when TR1 run control bit is not available i.e. when Timer 0 is in mode 3.

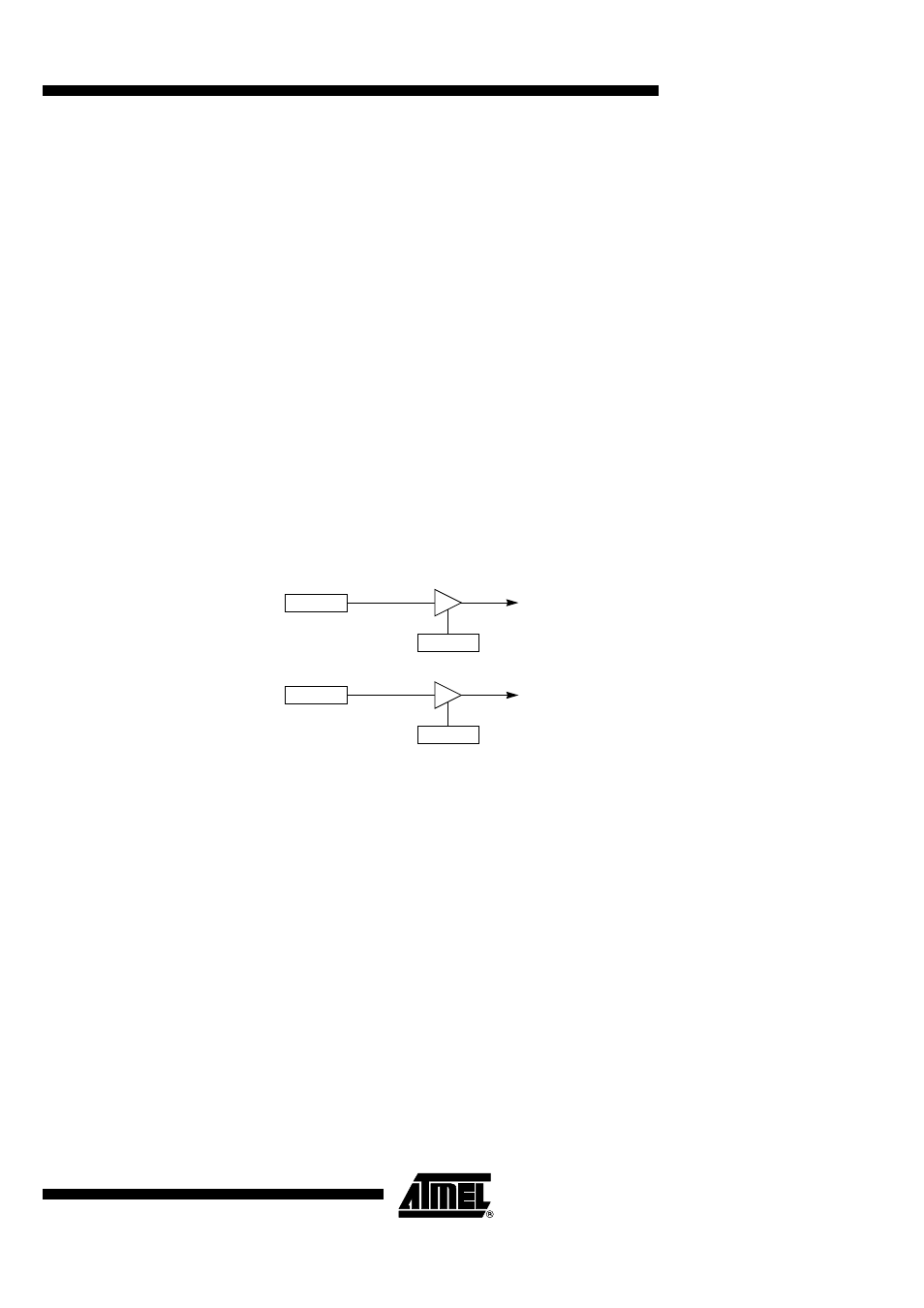

Interrupt

Each Timer handles one interrupt source that is the timer overflow flag TF0 or TF1. This

flag is set every time an overflow occurs. Flags are cleared when vectoring to the Timer

interrupt routine. Interrupts are enabled by setting ETx bit in IEN0 register. This

assumes interrupts are globally enabled by setting EA bit in IEN0 register.

Figure 37. Timer Interrupt System

TF0

TCON.5

ET0

IEN0.1

Timer 0

Interrupt Request

TF1

TCON.7

ET1

IEN0.3

Timer 1

Interrupt Request