E figure 91 s, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 132

132

AT8xC51SND1C

4109E–8051–06/03

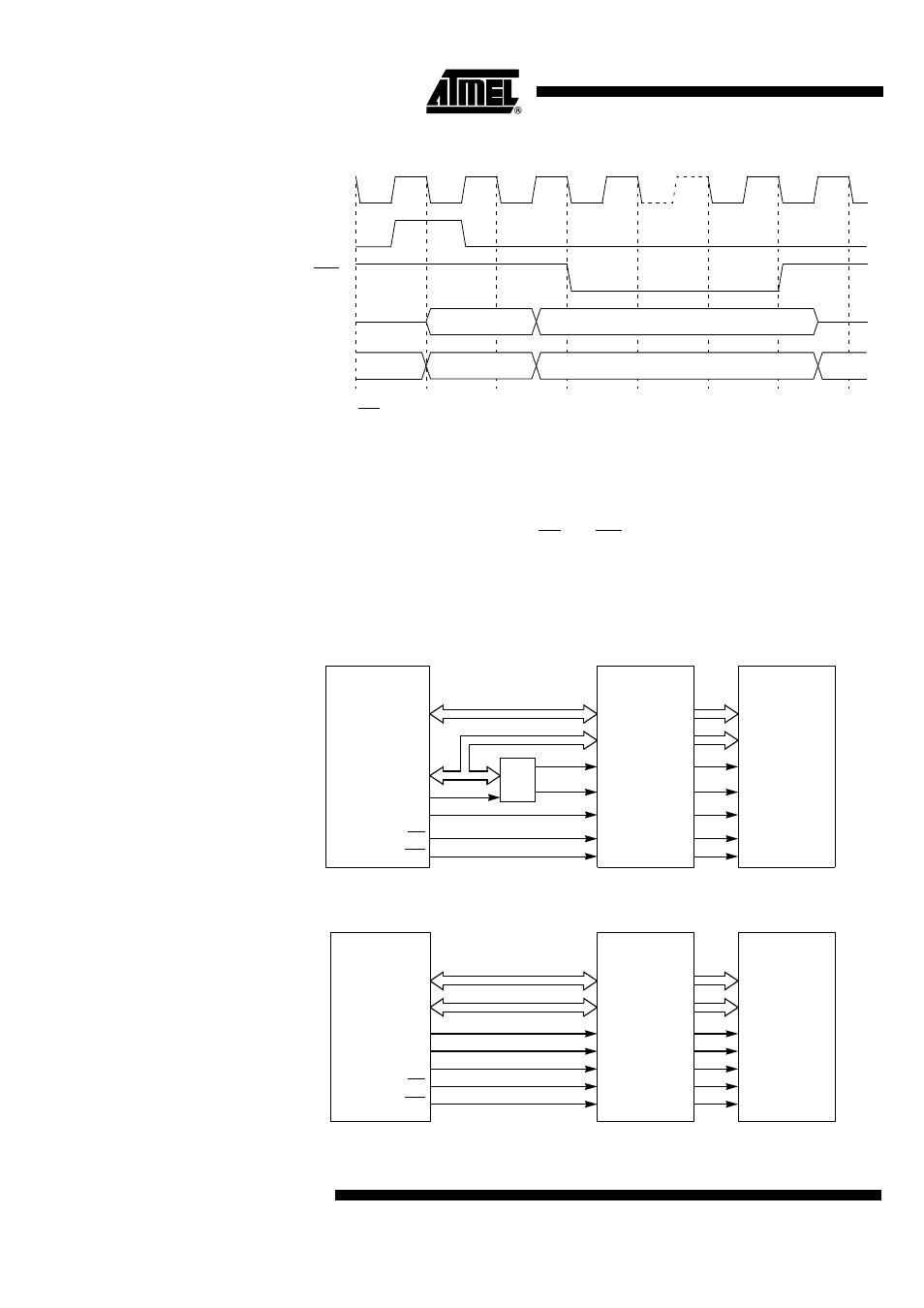

Figure 91. IDE Write Waveforms

Notes:

1.

WR

signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

3. When executing MOVX @DPTR instruction, if DPHDIS is set (Page Access Mode),

P2 outputs SFR content instead of DPH.

IDE Device Connection

Figure 92 and Figure 93 show 2 examples on how to interface up to 2 IDE devices to the

AT8xC51SND1C. In both examples P0 carries IDE low order data bits D7:0, P2 carries

IDE high order data bits D15:8, while RD and WR signals are respectively connected to

the IDE nIOR and nIOW signals. Other IDE control signals are generated by the exter-

nal address latch outputs in the first example while they are generated by some port

I/Os in the second one. Using an external latch will achieve higher transfer rate.

Figure 92. IDE Device Connection Example 1

Figure 93. IDE Device Connection Example 2

ALE

P0

P2

WR

(1)

DPL or Ri

D7:0

P2

CPU Clock

DPH or P2

(2),(3)

D15:8

P2

P2

P0

D15-8

A2:0

ALE

nIOW

nIOR

RD

WR

D7:0

nCS1:0

nRESET

D15-8

A2:0

nIOW

nIOR

D7:0

nCS1:0

nRESET

Latch

IDE Device 0

IDE Device 1

AT8xC51SND1C

Px.y

P2/A15:8

P0/AD7:0

D15-8

A2:0

P4.5

nIOW

nIOR

RD

WR

D7:0

nCS1:0

nRESET

D15-8

A2:0

nIOW

nIOR

D7:0

nCS1:0

nRESET

P4.2:0

P4.4:3

IDE Device 0

AT8xC51SND1C

IDE Device 1