D table 140. t, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 171

171

AT8xC51SND1C

4109E–8051–06/03

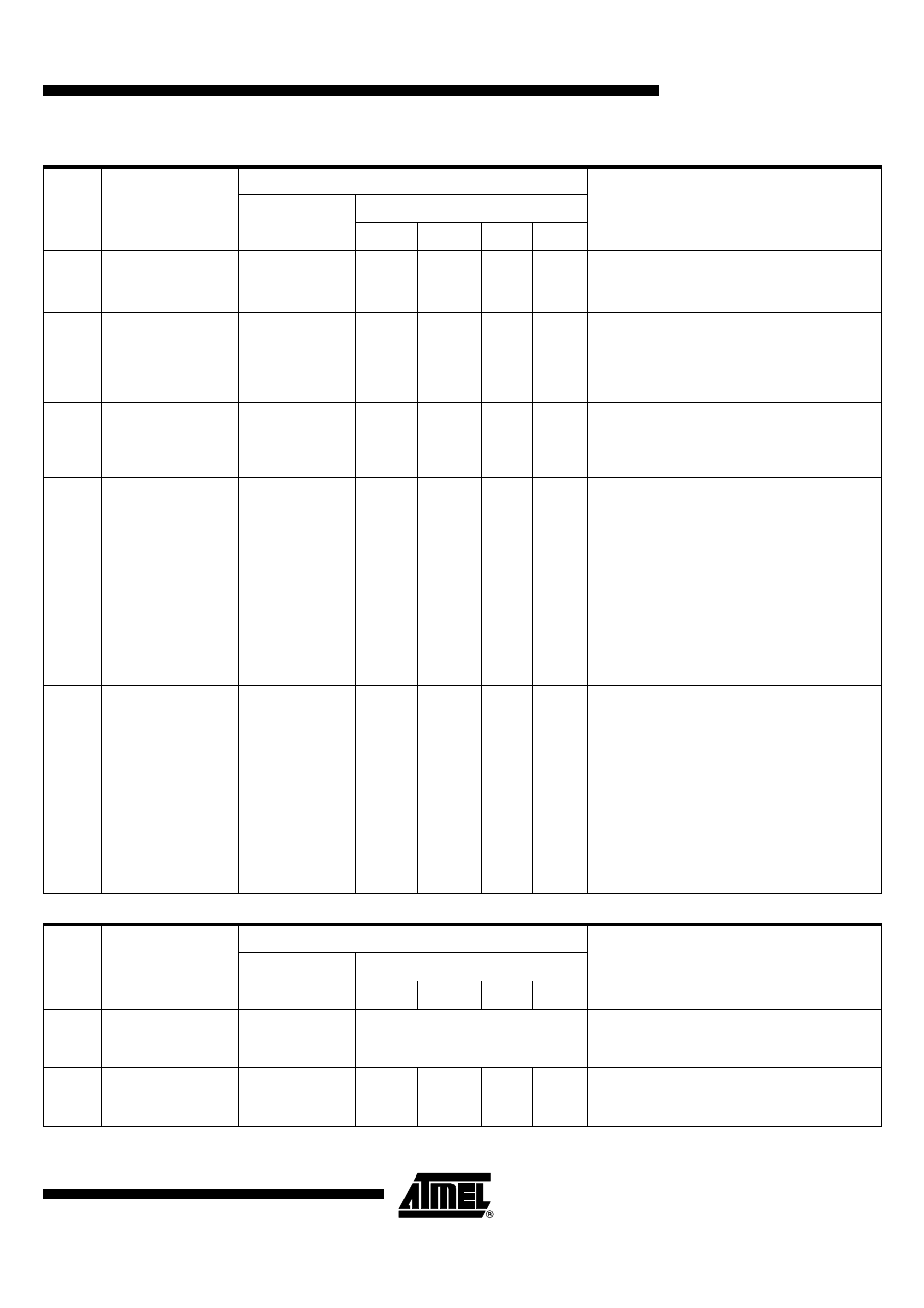

Table 140. Status for Slave Transmitter Mode

Status

Code

SSSTA

Status of the TWI Bus

and TWI Hardware

Application Software Response

Next Action Taken by TWI Hardware

To/From SSDAT

To SSCON

SSSTA

SSSTO

SSI

SSAA

A8h

Own SLA+R has been

received; ACK has

been returned

Write data Byte

Write data Byte

X

X

0

0

0

0

0

1

Last data Byte will be transmitted.

Data Byte will be transmitted.

B0h

Arbitration lost in

SLA+R/W as master;

own SLA+R has been

received; ACK has

been returned

Write data Byte

Write data Byte

X

X

0

0

0

0

0

1

Last data Byte will be transmitted.

Data Byte will be transmitted.

B8h

Data Byte in SSDAT

has been transmitted;

ACK has been

received

Write data Byte

Write data Byte

X

X

0

0

0

0

0

1

Last data Byte will be transmitted.

Data Byte will be transmitted.

C0h

Data Byte in SSDAT

has been transmitted;

NOT ACK has been

received

No SSDAT action

No SSDAT action

No SSDAT action

No SSDAT action

0

0

1

1

0

0

0

0

0

0

0

0

0

1

0

1

Switched to the not addressed slave mode; no

recognition of own SLA or GCA.

Switched to the not addressed slave mode; own

SLA will be recognized; GCA will be recognized if

SSGC = logic 1.

Switched to the not addressed slave mode; no

recognition of own SLA or GCA. A START condition

will be transmitted when the bus becomes free.

Switched to the not addressed slave mode; own

SLA will be recognized; GCA will be recognized if

SSGC = logic 1. A START condition will be

transmitted when the bus becomes free.

C8h

Last data Byte in

SSDAT has been

transmitted

(SSAA= 0); ACK has

been received

No SSDAT action

No SSDAT action

No SSDAT action

No SSDAT action

0

0

1

1

0

0

0

0

0

0

0

0

0

1

0

1

Switched to the not addressed slave mode; no

recognition of own SLA or GCA.

Switched to the not addressed slave mode; own

SLA will be recognized; GCA will be recognized if

SSGC = logic 1.

Switched to the not addressed slave mode; no

recognition of own SLA or GCA. A START condition

will be transmitted when the bus becomes free.

Switched to the not addressed slave mode; own

SLA will be recognized; GCA will be recognized if

SSGC = logic 1. A START condition will be

transmitted when the bus becomes free.

Table 141. Status for Miscellaneous States

Status

Code

SSSTA

Status of the TWI Bus

and TWI Hardware

Application Software Response

Next Action Taken by TWI Hardware

To/From SSDAT

To SSCON

SSSTA

SSSTO

SSI

SSAA

F8h

No relevant state

information available;

SSI = 0

No SSDAT action

No SSCON action

Wait or proceed current transfer.

00h

Bus error due to an

illegal START or STOP

condition

No SSDAT action

0

1

0

X

Only the internal hardware is affected, no STOP

condition is sent on the bus. In all cases, the bus is

released and SSSTO is reset.