Description, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 147

147

AT8xC51SND1C

4109E–8051–06/03

Description

The SPI controller interfaces with the C51 core through three special function registers:

SPCON, the SPI control register (see Table 132); SPSTA, the SPI status register (see

Table 133); and SPDAT, the SPI data register (see Table 134).

Master Mode

The SPI operates in master mode when the MSTR bit in SPCON is set.

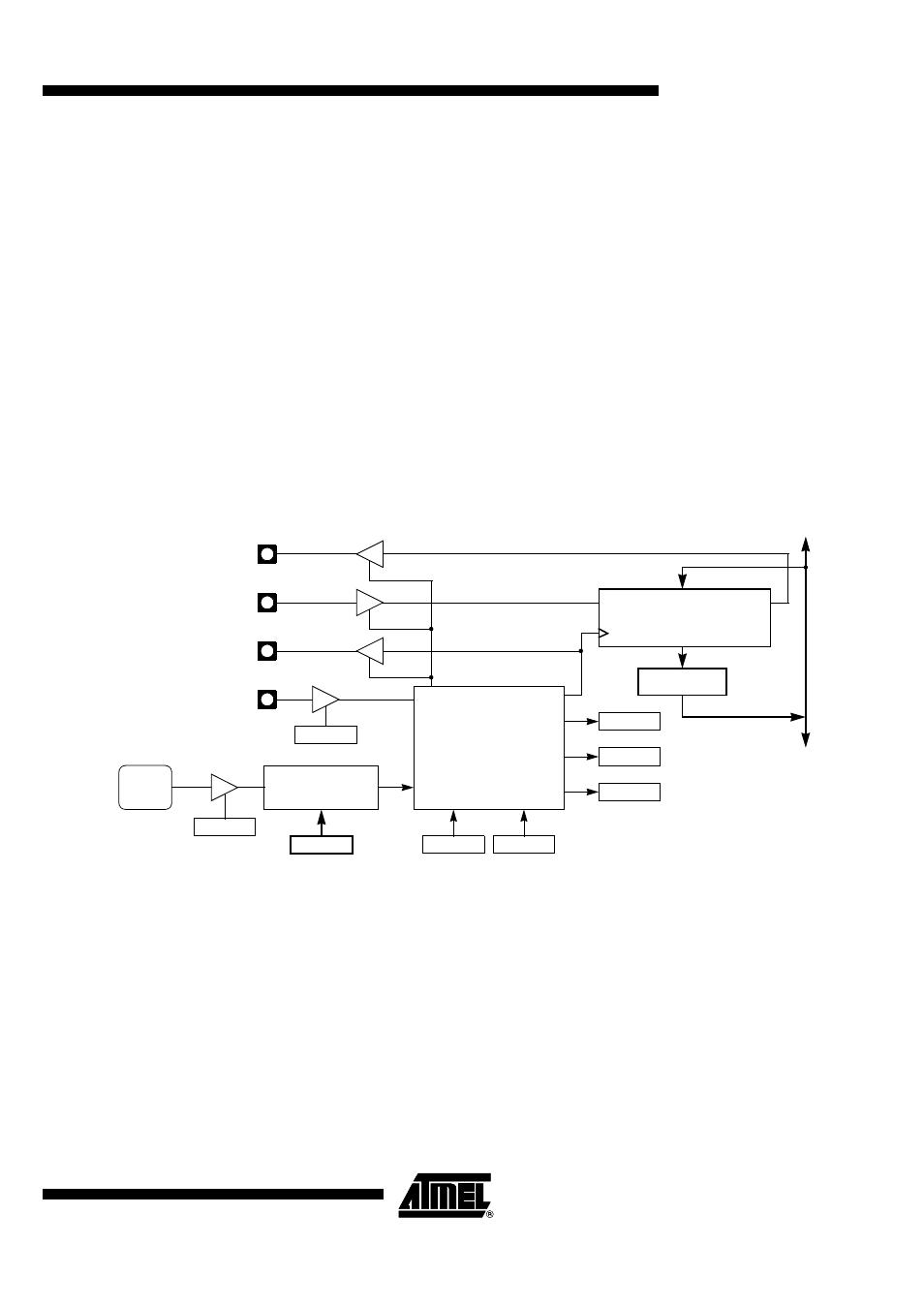

Figure 113 shows the SPI block diagram in master mode. Only a master SPI module

can initiate transmissions. Software begins the transmission by writing to SPDAT. Writ-

ing to SPDAT writes to the shift register while reading SPDAT reads an intermediate

register updated at the end of each transfer.

The Byte begins shifting out on the MOSI pin under the control of the bit rate generator.

This generator also controls the shift register of the slave peripheral through the SCK

output pin. As the Byte shifts out, another Byte shifts in from the slave peripheral on the

MISO pin. The Byte is transmitted most significant bit (MSB) first. The end of transfer is

signaled by SPIF being set.

When the AT8xC51SND1C is the only master on the bus, it can be useful not to use

SS# pin and get it back to I/O functionality. This is achieved by setting SSDIS bit in

SPCON.

Figure 113. SPI Master Mode Block Diagram

Note:

MSTR bit in SPCON is set to select master mode.

Bit Rate Generator

SPR2:0

SPCON

MOSI/P4.1

MISO/P4.0

SCK/P4.2

CPOL

SPCON.3

SPEN

SPCON.6

CPHA

SPCON.2

PER

CLOCK

8-bit Shift Register

SPDAT WR

I

Q

In

te

rnal

Bus

SPDAT RD

Control and Clock Logic

MODF

SPSTA.4

SS#/P4.3

SSDIS

SPCON.5

WCOL

SPSTA.6

SPIF

SPSTA.7