Figure 124 s, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 159

159

AT8xC51SND1C

4109E–8051–06/03

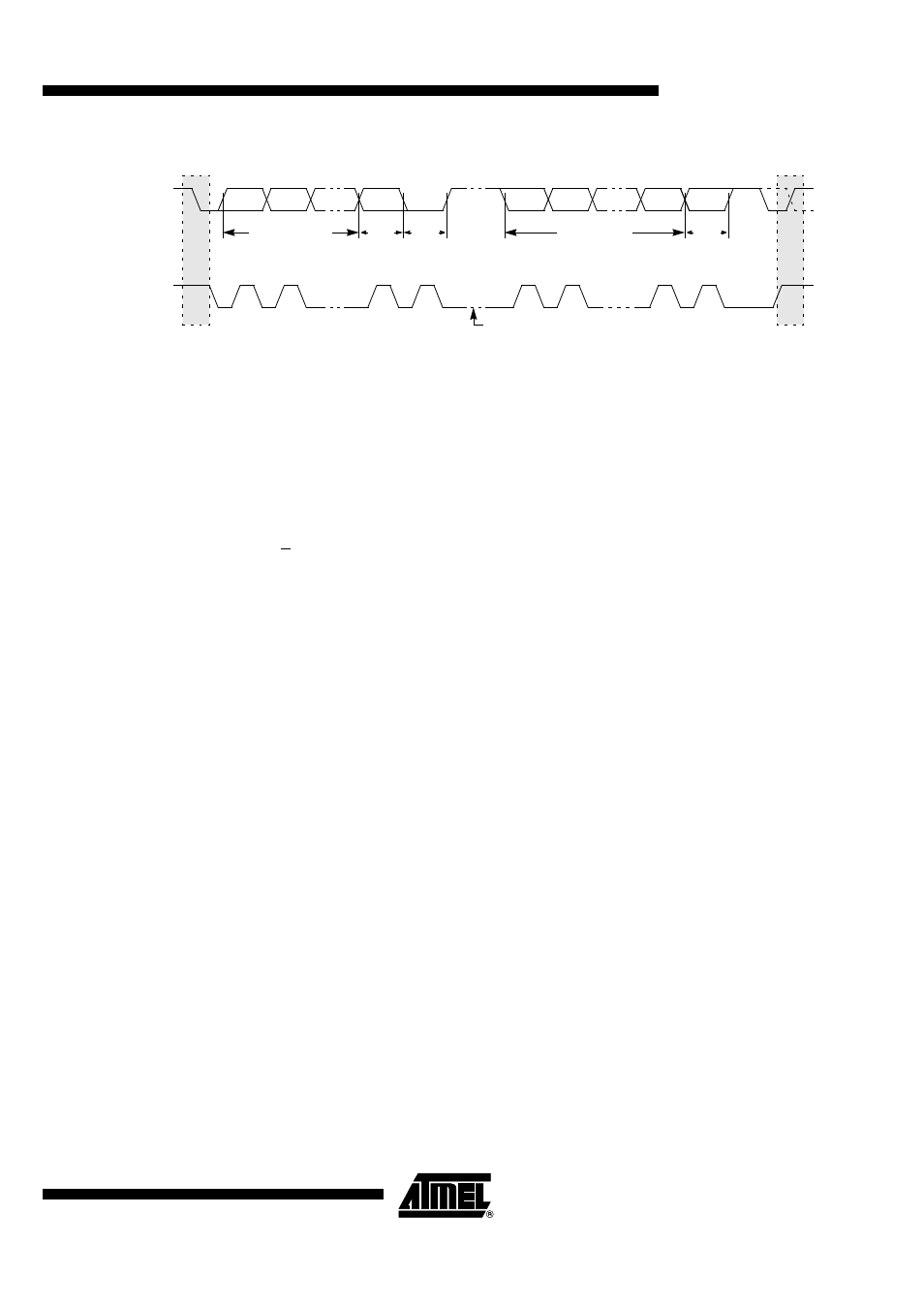

Figure 124. Complete Data Transfer on TWI Bus

The four operating modes are:

•

Master transmitter

•

Master receiver

•

Slave transmitter

•

Slave receiver

Data transfer in each mode of operation are shown in Figure 125 through Figure 128.

These figures contain the following abbreviations:

A

Acknowledge bit (low level at SDA)

A

Not acknowledge bit (high level on SDA)

Data

8-bit data Byte

S

START condition

P

STOP condition

MR

Master Receive

MT

Master Transmit

SLA

Slave Address

GCA

General Call Address (00h)

R

Read bit (high level at SDA)

W

Write bit (low level at SDA)

In Figure 125 through Figure 128, circles are used to indicate when the serial interrupt

flag is set. The numbers in the circles show the status code held in SSSTA. At these

points, a service routine must be executed to continue or complete the serial transfer.

These service routines are not critical since the serial transfer is suspended until the

serial interrupt flag is cleared by software.

When the serial interrupt routine is entered, the status code in SSSTA is used to branch

to the appropriate service routine. For each status code, the required software action

and details of the following serial transfer are given in Table 136 through Table 128.

S

Slave Address

SCL

SDA

MSB

R/W

direction

ACK

signal

Nth data Byte

ACK

signal

P/S

bit

from

receiver

from

receiver

1

2

8

9

1

2

8

9

Clock Line Held Low While Serial Interrupts Are Serviced