Interrupt, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 124

124

AT8xC51SND1C

4109E–8051–06/03

Interrupt

Description

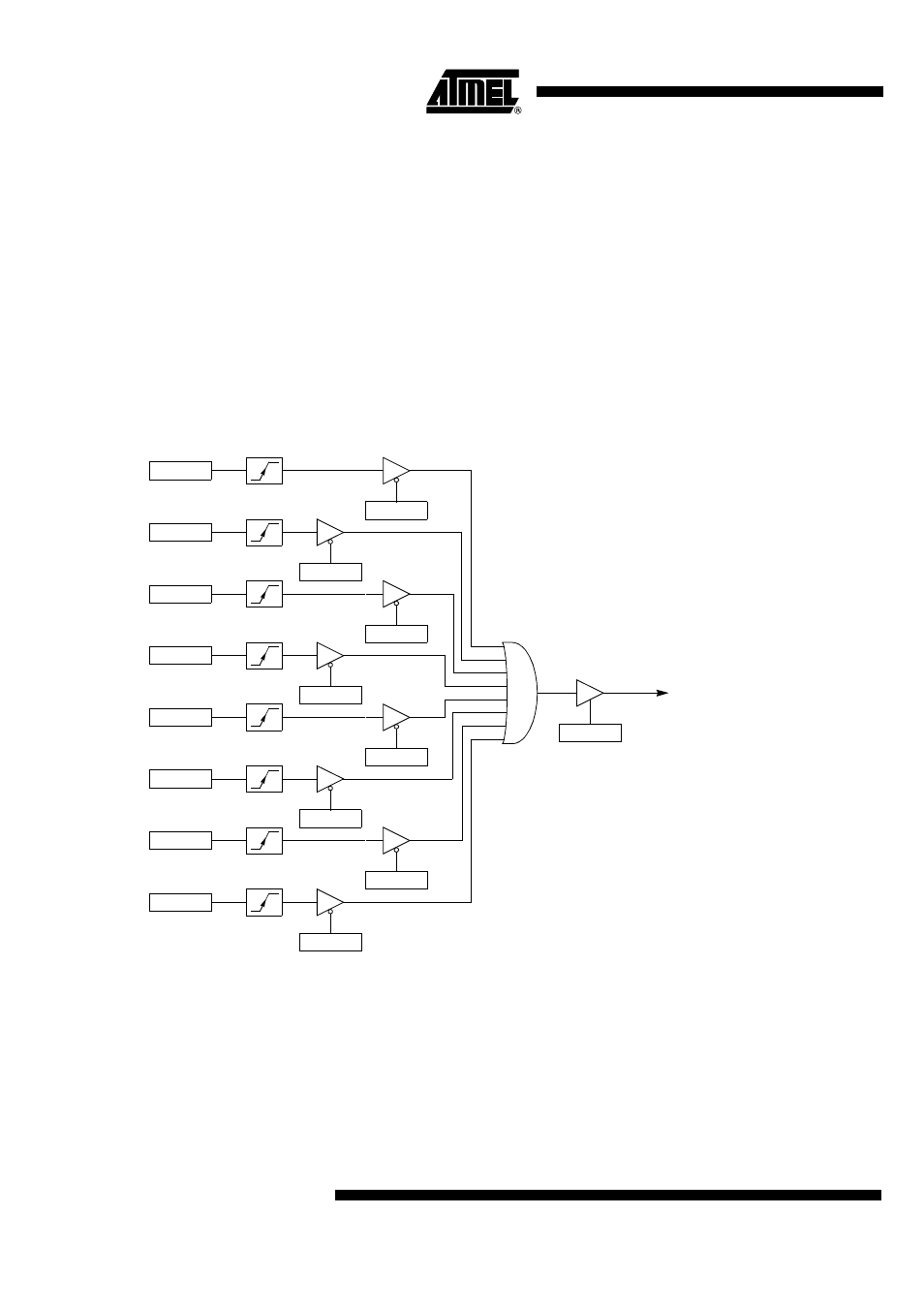

As shown in Figure 89, the MMC controller implements eight interrupt sources reported

in MCBI, EORI, EOCI, EOFI, F2FI, F1FI, and F2EI flags in MMCINT register. These

flags are detailed in the previous sections.

All these sources are maskable separately using MCBM, EORM, EOCM, EOFM, F2FM,

F1FM, and F2EM mask bits respectively in MMMSK register.

The interrupt request is generated each time an unmasked flag is set, and the global

MMC controller interrupt enable bit is set (EMMC in IEN1 register).

Reading the MMINT register automatically clears the interrupt flags (acknowledgment).

This implies that register content must be saved and tested interrupt flag by interrupt

flag to be sure not to forget any interrupts.

Figure 89. MMC Controller Interrupt System

MMC Interface

Interrupt Request

MCBI

MMINT.7

EOCM

MMMSK.5

EMMC

IEN1.0

MCBM

MMMSK.7

EORM

MMMSK.6

EOFI

MMINT.4

F2FM

MMMSK.3

EOFM

MMMSK.4

EORI

MMINT.6

F2FI

MMINT.3

EOCI

MMINT.5

F2EM

MMMSK.1

F1FM

MMMSK.2

F1EI

MMINT.0

F1EM

MMMSK.0

F1FI

MMINT.2

F2EI

MMINT.1