At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 100

100

AT8xC51SND1C

4109E–8051–06/03

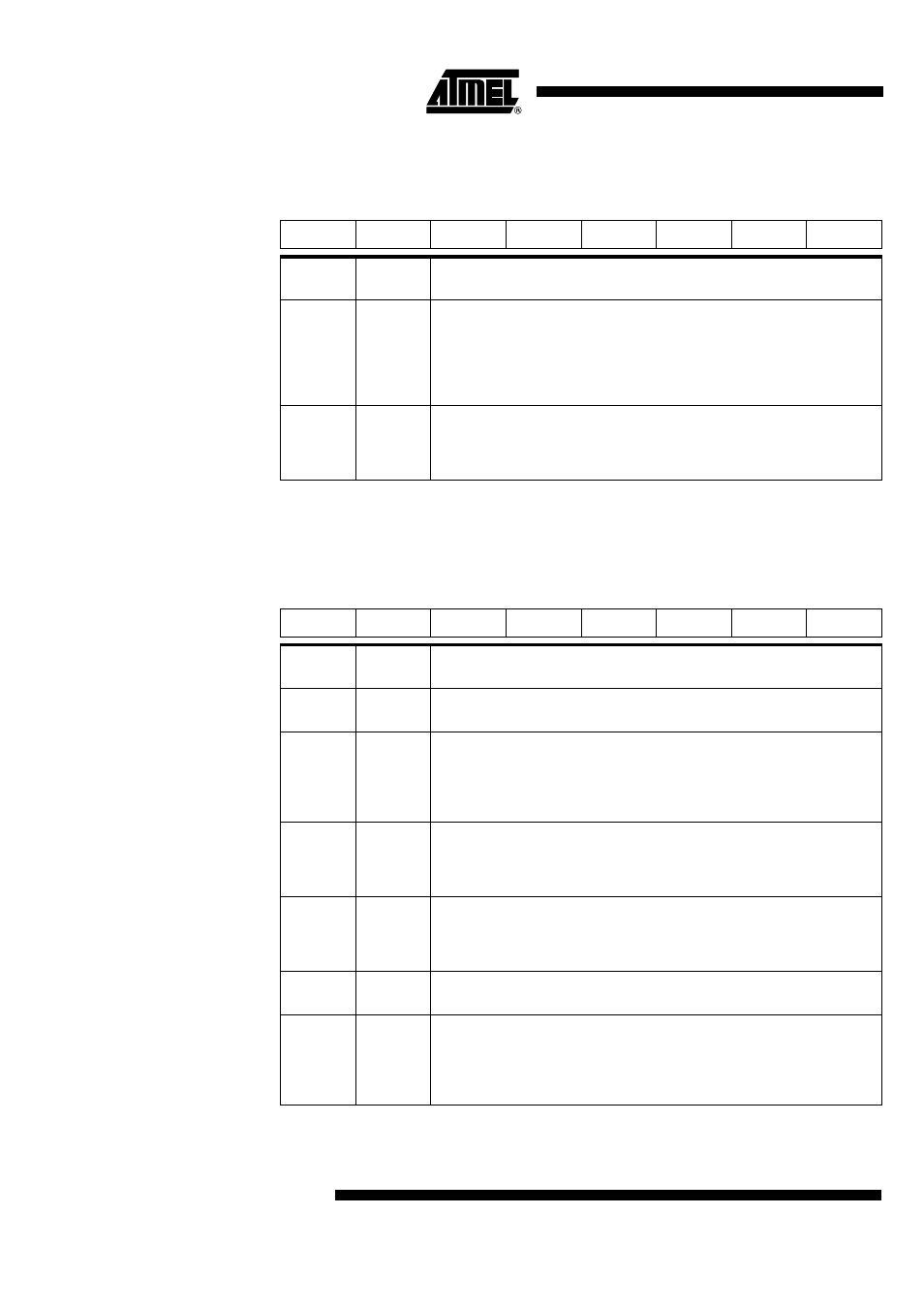

Table 91. USBADDR Register

USBADDR (S:C6h) – USB Address Register

Reset Value = 0000 0000b

Table 92. USBINT Register

USBINT (S:BDh) – USB Global Interrupt Register

Reset Value = 0000 0000b

7

6

5

4

3

2

1

0

FEN

UADD6

UADD5

UADD4

UADD3

UADD2

UADD1

UADD0

Bit

Number

Bit

Mnemonic

Description

7

FEN

Function Enable Bit

Set to enable the function. The device firmware should set this bit after it has

received a USB reset and participate in the following configuration process with

the default address (FEN is reset to 0).

Cleared by hardware at power-up, should not be cleared by the device firmware

once set.

6 - 0

UADD6:0

USB Address Bits

This field contains the default address (0) after power-up or USB bus reset.

It should be written with the value set by a SET_ADDRESS request received by

the device firmware.

7

6

5

4

3

2

1

0

-

-

WUPCPU

EORINT

SOFINT

-

-

SPINT

Bit

Number

Bit

Mnemonic

Description

7 - 6

-

Reserved

The value read from these bits is always 0. Do not set these bits.

5

WUPCPU

Wake Up CPU Interrupt Flag

Set by hardware when the USB controller is in SUSPEND state and is re-

activated by a non-idle signal from USB line (not by an upstream resume). This

triggers a USB interrupt when EWUPCPU is set in the USBIEN.

Cleared by software after re-enabling all USB clocks.

4

EORINT

End of Reset Interrupt Flag

Set by hardware when a End of Reset has been detected by the USB controller.

This triggers a USB interrupt when EEORINT is set in USBIEN.

Cleared by software.

3

SOFINT

Start of Frame Interrupt Flag

Set by hardware when an USB Start of Frame packet (SOF) has been properly

received. This triggers a USB interrupt when ESOFINT is set in USBIEN.

Cleared by software.

2 - 1

-

Reserved

The value read from these bits is always 0. Do not set these bits.

0

SPINT

Suspend Interrupt Flag

Set by hardware when a USB Suspend (Idle bus for three frame periods: a J

state for 3 ms) is detected. This triggers a USB interrupt when ESPINT is set in

USBIEN.

Cleared by software.