At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 106

106

AT8xC51SND1C

4109E–8051–06/03

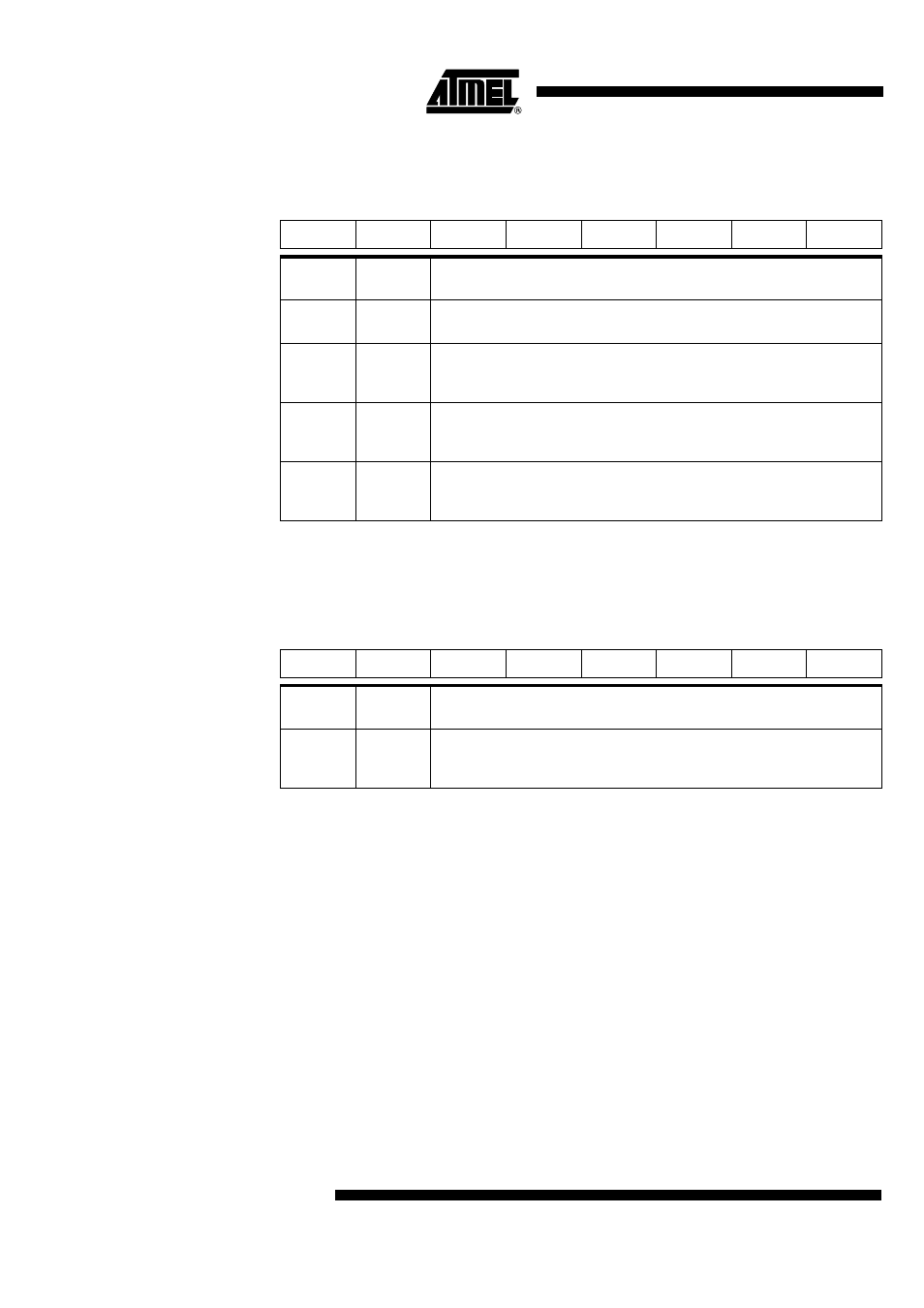

Table 99. UEPIEN Register

UEPIEN (S:C2h) – USB Endpoint Interrupt Enable Register

Reset Value = 0000 0000b

Table 100. UEPDATX Register

UEPDATX (S:CFh) –

USB Endpoint X FIFO Data Register (X = EPNUM set in UEPNUM)

Reset Value = XXh

7

6

5

4

3

2

1

0

-

-

-

-

-

EP2INTE

EP1INTE

EP0INTE

Bit

Number

Bit

Mnemonic

Description

7 - 3

-

Reserved

The value read from these bits is always 0. Do not set these bits.

2

EP2INTE

Endpoint 2 Interrupt Enable Bit

Set to enable the interrupts for endpoint 2.

Clear this bit to disable the interrupts for endpoint 2.

1

EP1INTE

Endpoint 1 Interrupt Enable Bit

Set to enable the interrupts for the endpoint 1.

Clear to disable the interrupts for the endpoint 1.

0

EP0INTE

Endpoint 0 Interrupt Enable Bit

Set to enable the interrupts for the endpoint 0.

Clear to disable the interrupts for the endpoint 0.

7

6

5

4

3

2

1

0

FDAT7

FDAT6

FDAT5

FDAT4

FDAT3

FDAT2

FDAT1

FDAT0

Bit

Number

Bit

Mnemonic

Description

7 - 0

FDAT7:0

Endpoint X FIFO Data

Data Byte to be written to FIFO or data Byte to be read from the FIFO, for the

Endpoint X (see EPNUM).