Interrupt, At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 151

151

AT8xC51SND1C

4109E–8051–06/03

Interrupt

The SPI handles 2 interrupt sources that are the “end of transfer” and the “mode fault”

flags.

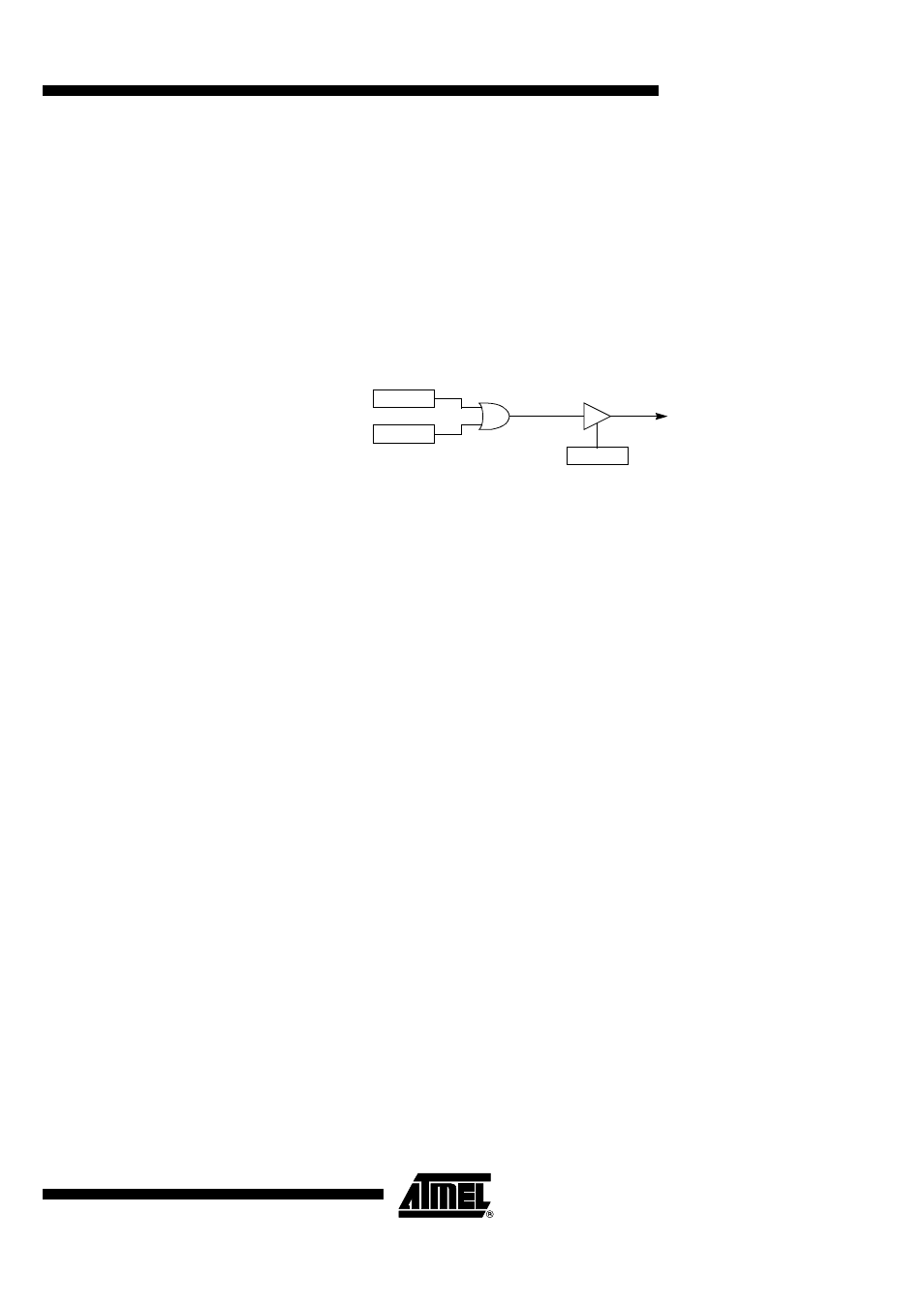

As shown in Figure 118, these flags are combined toghether to appear as a single inter-

rupt source for the C51 core. The SPIF flag is set at the end of an 8-bit shift in and out

and is cleared by reading SPSTA and then reading from or writing to SPDAT.

The MODF flag is set in case of mode fault error and is cleared by reading SPSTA and

then writing to SPCON.

The SPI interrupt is enabled by setting ESPI bit in IEN1 register. This assumes inter-

rupts are globally enabled by setting EA bit in IEN0 register.

Figure 118. SPI Interrupt System

ESPI

IEN1.2

SPI Controller

Interrupt Request

SPIF

SPSTA.7

MODF

SPSTA.4

See also other documents in the category Rainbow Electronics Sensors:

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)