At8xc51snd1c – Rainbow Electronics AT89C51SND1C User Manual

Page 102

102

AT8xC51SND1C

4109E–8051–06/03

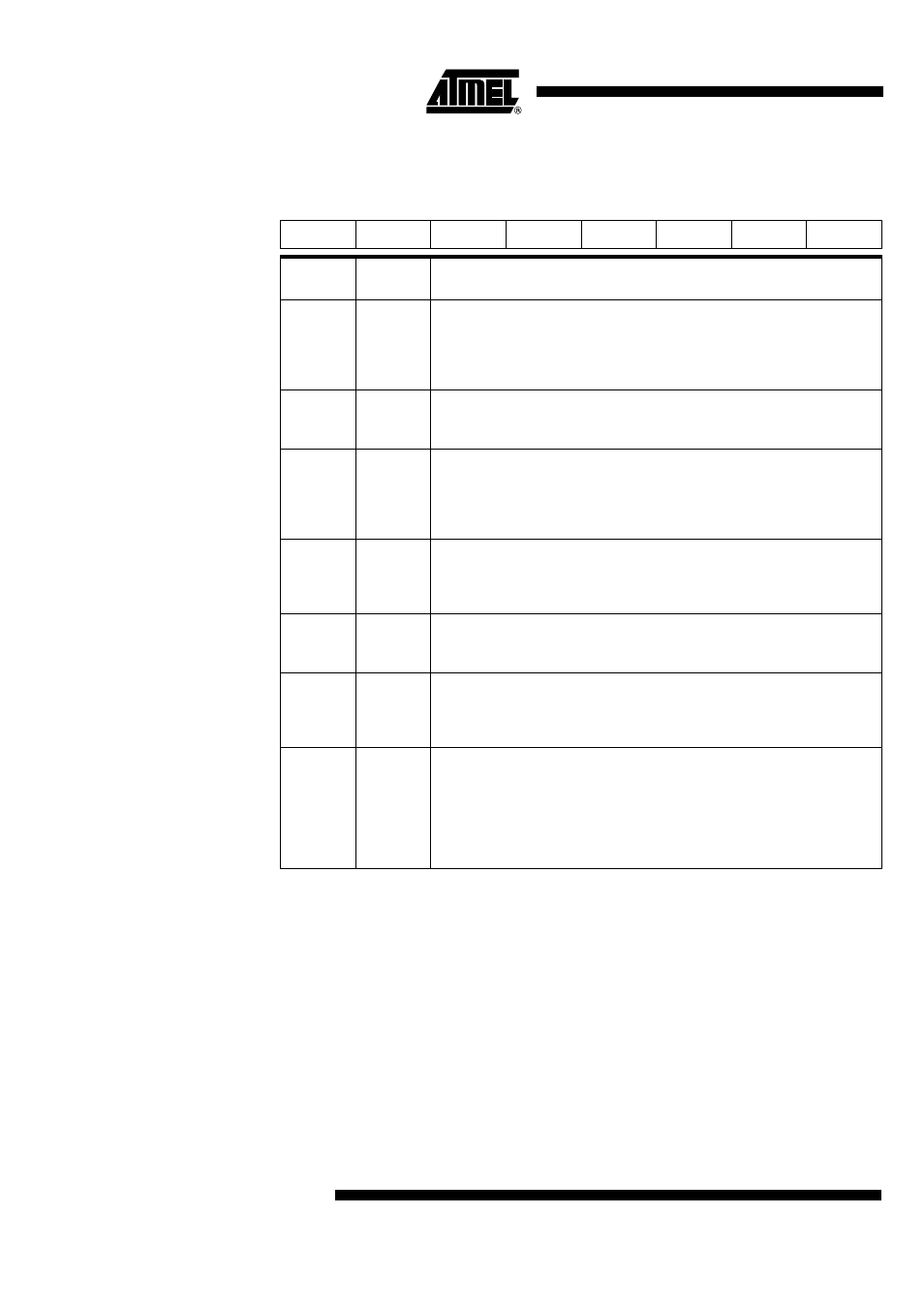

Table 95. UEPCONX Register

UEPCONX (S:D4h) – USB Endpoint X Control Register (X = EPNUM set in UEPNUM)

Reset Value = 1000 0000b

7

6

5

4

3

2

1

0

EPEN

NAKIEN

NAKOUT

NAKIN

DTGL

EPDIR

EPTYPE1

EPTYPE0

Bit

Number

Bit

Mnemonic

Description

7

EPEN

Endpoint Enable Bit

Set to enable the endpoint according to the device configuration. Endpoint 0

should always be enabled after a hardware or USB bus reset and participate in

the device configuration.

Clear to disable the endpoint according to the device configuration.

6

NAKIEN

NAK Interrupt enable

Set this bit to enable NAK IN or NAK OUT interrupt.

Clear this bit to disable NAK IN or NAK OUT Interrupt.

5

NAKOUT

NAK OUT received

This bit is set by hardware when an NAK handshake has been sent in response

of a OUT request from the Host. This triggers a USB interrupt when NAKIEN is

set.

This bit should be cleared by software.

4

NAKIN

NAK IN received

This bit is set by hardware when an NAK handshake has been sent in response

of a IN request from the Host. This triggers a USB interrupt when NAKIEN is set.

This bit should be cleared by software.

3

DTGL

Data Toggle Status Bit (Read-only)

Set by hardware when a DATA1 packet is received.

Cleared by hardware when a DATA0 packet is received.

2

EPDIR

Endpoint Direction Bit

Set to configure IN direction for Bulk, Interrupt and Isochronous endpoints.

Clear to configure OUT direction for Bulk, Interrupt and Isochronous endpoints.

This bit has no effect for Control endpoints.

1-0

EPTYPE1:0

Endpoint Type Bits

Set this field according to the endpoint configuration (Endpoint 0 should always

be configured as Control):

00

Control endpoint

01

Isochronous endpoint

10

Bulk endpoint

11

Interrupt endpoint