Internal operations 100, Prosec t2n – Toshiba T2N User Manual

Page 113

2.INTERNAL OPERATIONS

100

PROSEC T2N

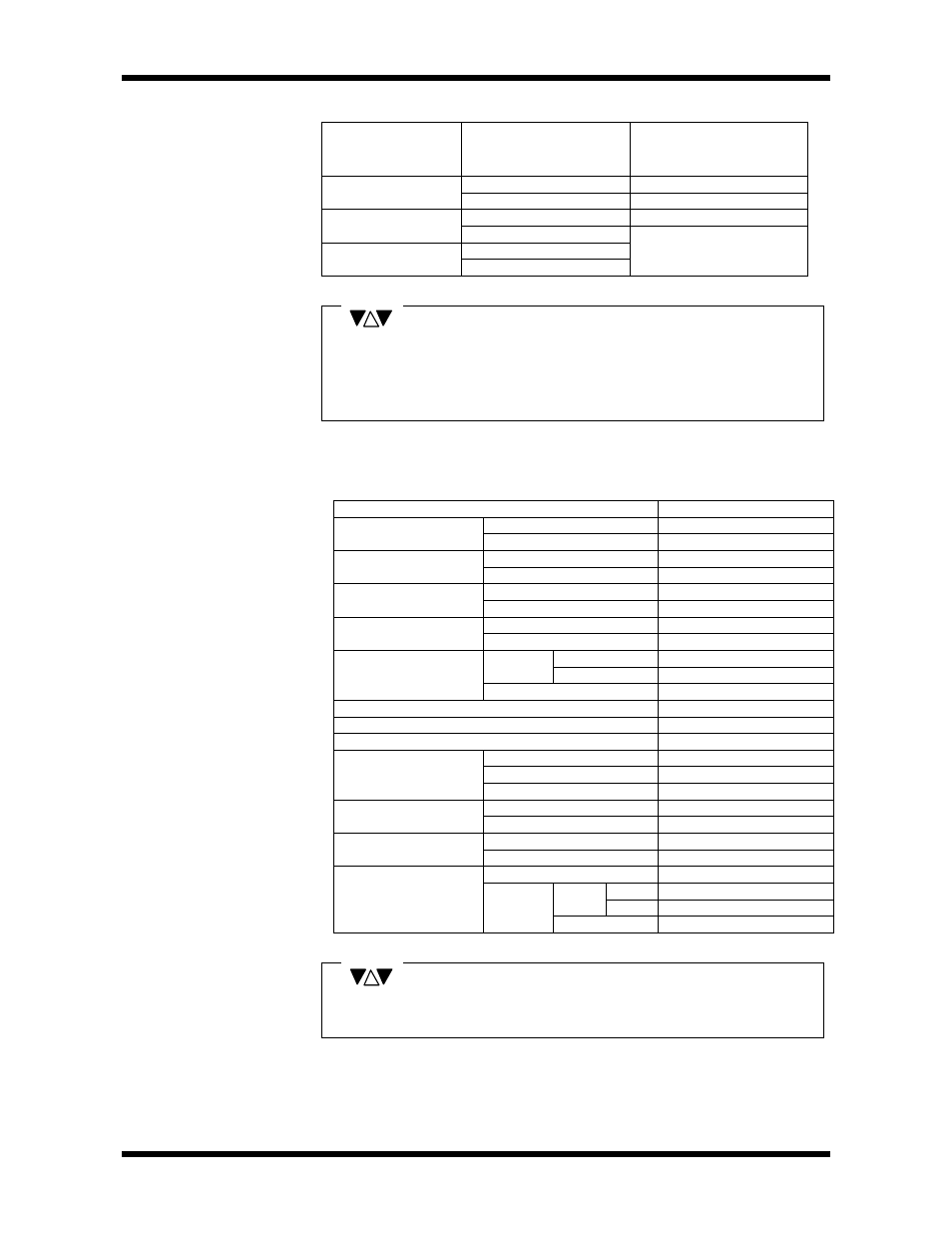

Performance table of initial load(power on)

Operation mode

switch

ROM/RAM

switch

(DIP SW.2)

Initial load

performance

OFF(ROM)

performed

HALT

ON(RAM)

not performed

OFF(ROM)

performed

RUN

ON(RAM)

OFF(ROM)

P-RUN

ON(RAM)

not performed

When the initial load is performed, the contents of EEPROM is

transfered to RAM. That is, the contents of RAM is overwritten.

Therefore it is necessary to write to EEPROM before power OFF

when the user program is changed.

User data initialization

The user data (registers and devices) is initialized according to the conditions

in the following table. :

Register/Device

Initialization

Input register/device

Force area

retained

(XW/X)

Other area except the above

0 clear

Output register/device

Force area

retained

(YW/Y)

Other area except the above

0 clear

Link register/device

Force transmission area

retained

(W/Z)

Other area except the above

0 clear

Link relay register/relay

Force transmission area

retained

(LW/L)

Other area except the above

0 clear

Special register/device

SW0-063

CPU specified

Initialization

(SW/S)

User specified

retained

SW064-

0 clear

File register(F)

retained

Expanded file register

0 clear

Index register(I,J,K)

0 clear

Auxiliary register/device Specified retentive area

retained

(RW/R)

Force area

retained

Other area except the above

0 clear

Timer register/device

Specified retentive area

retained

(T/T.)

Other area except the above

0 clear

Counter register/device

Specified retentive area

retained

(C/C.)

Other area except the above

0 clear

Specified retentive area

retained

Normal

0 clear

D0-D2047

P-RUN

retained

Data register

(D)

Other area

except the

above

D2048-

0 clear

Refer to 5.6 Debug Support Function for forced functions.

Refer to Part.3 2.2 for power failure support specification.

User program check

The content of the user program is checked by the main memory (RAM) on

BCC.

NOTE

NOTE

…

†