Texas Instruments TMS320C64x DSP User Manual

Page 302

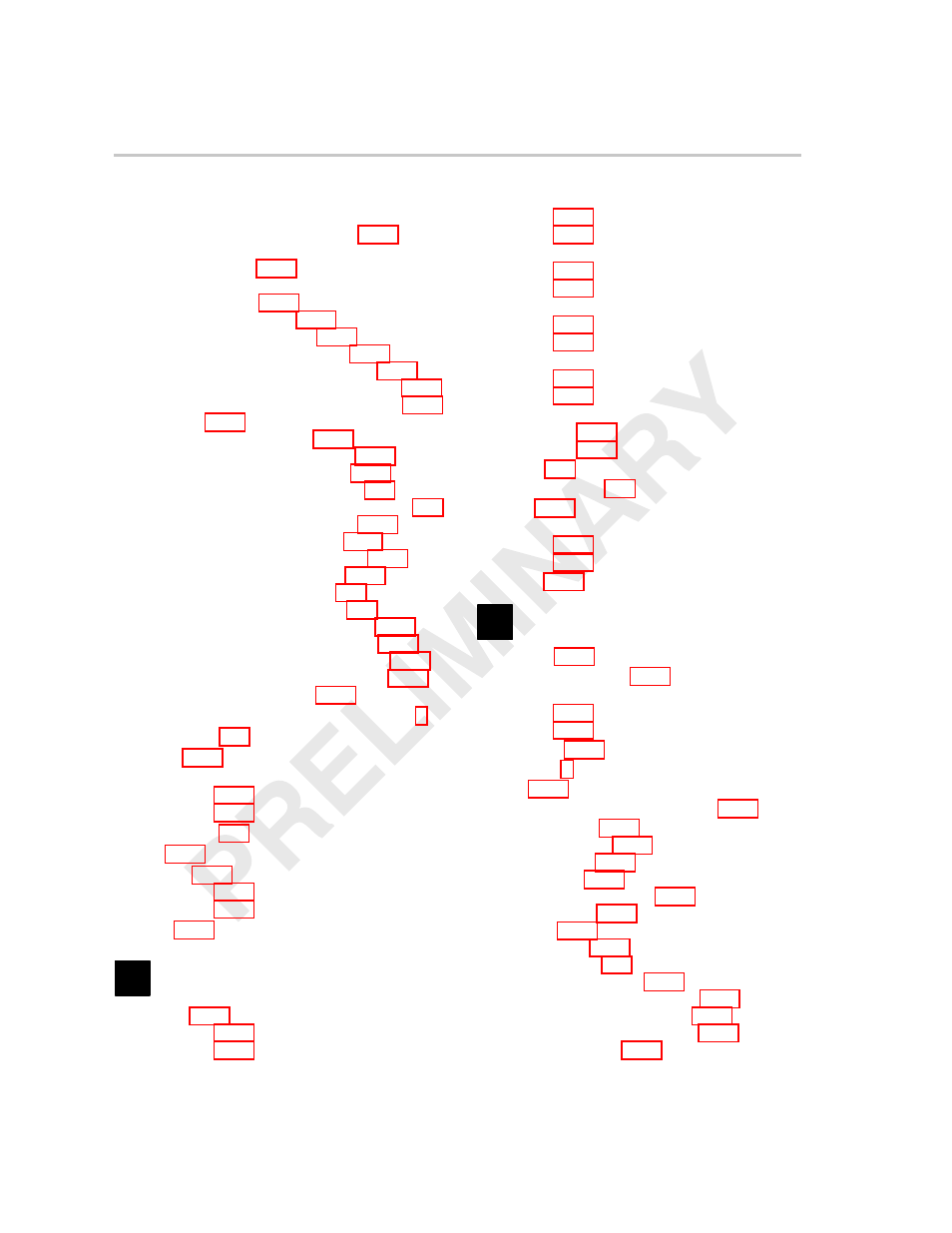

Index

Index-6

SPRU629

registers (continued)

video display

frame size register (VDFRMSZ)

horizontal blanking register

(VDHBLNK)

horizontal synchronization register

(VDHSYNC)

recommended values

status register (VDSTAT)

threshold register (VDTHRLD)

vertical interrupt register (VDVINT)

Y FIFO destination register A (YDSTA)

Y FIFO destination register B (YDSTB)

video port

control register (VPCTL)

interrupt enable register (VPIE)

interrupt status register (VPIS)

peripheral control register (PCR)

peripheral identification register (VPPID)

pin data clear register (PDCLR)

pin data input register (PDIN)

pin data output register (PDOUT)

pin data set register (PDSET)

pin direction register (PDIR)

pin function register (PFUNC)

pin interrupt clear register (PICLR)

pin interrupt enable register (PIEN)

pin interrupt polarity register (PIPOL)

pin interrupt status register (PISTAT)

status register (VPSTAT)

related documentation from Texas Instruments

reset operation

RESMPL

RESMPL bit

in VCACTL

in VCBCTL

REVISION bits

RGBX

RSTCH bit

in VCACTL

in VCBCTL

RSYNC

S

SCALE bit

in VCACTL

in VCBCTL

SERRA bit

in VPIE

in VPIS

SERRB bit

in VPIE

in VPIS

SFDA bit

in VPIE

in VPIS

SFDB bit

in VPIE

in VPIS

SFDE bit

in VCACTL

in VCBCTL

SOFT bit

software port reset

SSE bit

STC bit

in VPIE

in VPIS

STEN bit

T

TCKEN bit

throughput and latency

TICK bit

in VPIE

in VPIS

TICKCT bits

trademarks

TSI bit

TSI capture control register (TSICTL)

TSI capture mode

capture selection

capturing data

data capture

data capture notification

error detection

features

FIFO overrun

mode selection

reading from the FIFO

synchronizing the system clock

timestamp format (big endian)

timestamp format (little endian)

writing to the FIFO