15 tsi system time clock msb register (tsistclkm) – Texas Instruments TMS320C64x DSP User Manual

Page 139

Video Capture Registers

3-77

Video Capture Port

SPRU629

3.13.15

TSI System Time Clock MSB Register (TSISTCLKM)

The transport stream interface system time clock MSB register (TSISTCLKM)

contains the most-significant bit (MSB) of the program clock reference (PCR)

and the 9 bits of the PCR extension. The system time clock value is obtained

by reading TSISTCLKM and TSISTCLKL. TSISTCLKM is shown in

Figure 3–43 and described in Table 3–28.

The PCRE value changes at a 27-MHz rate and is probably not reliably read

by the DSP. The PCRM bit normally changes at a 10.5-

µ

Hz rate (every

26 hours).

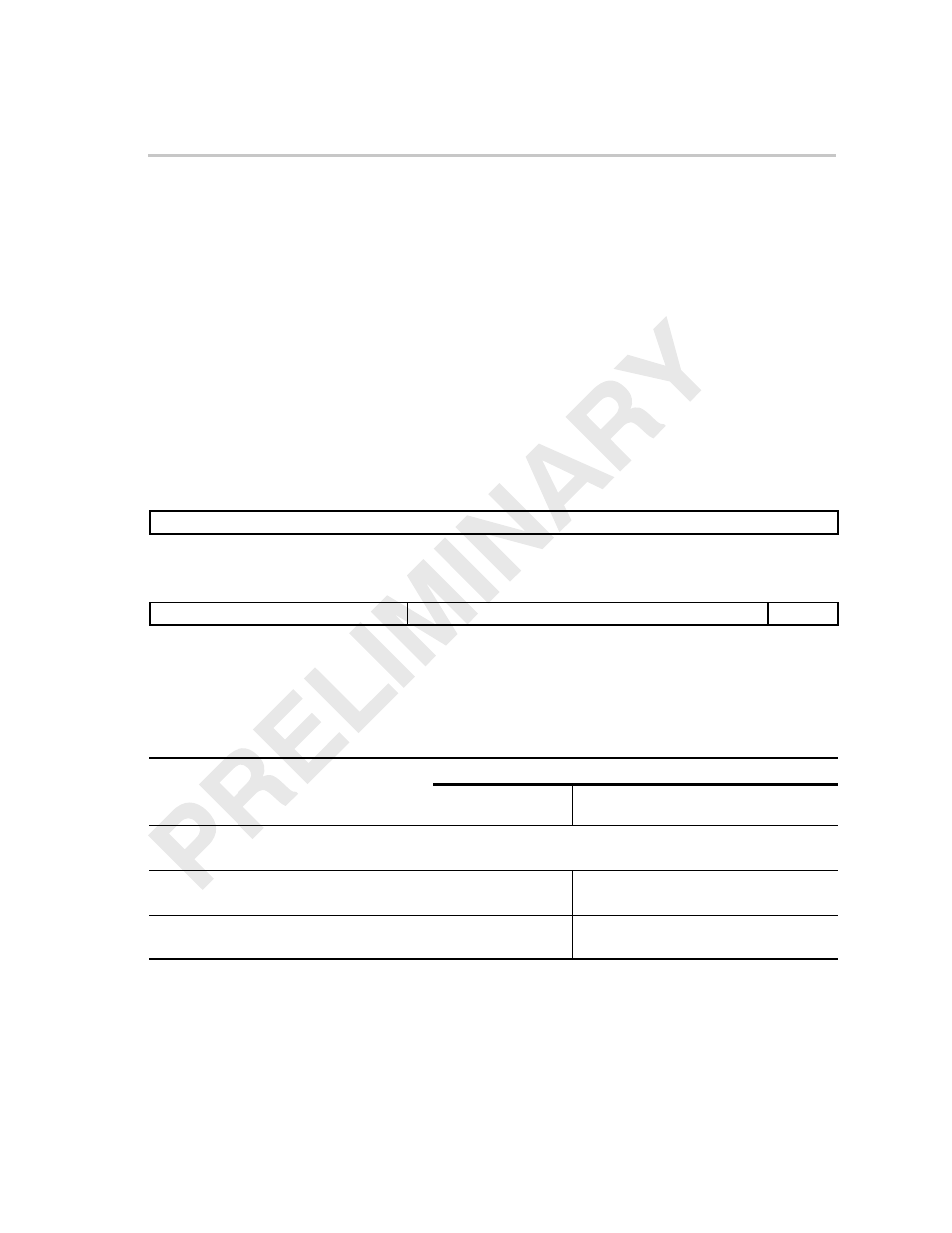

Figure 3–43. TSI System Time Clock MSB Register (TSISTCLKM)

31

16

Reserved

R-0

15

10

9

1

0

Reserved

PCRE

PCRM

R-0

R/W-0

R/W-0

Legend: R = Read only; R/W = Read/Write; -n = value after reset

Table 3–28. TSI System Time Clock MSB Register (TSISTCLKM) Field Descriptions

Description

Bit

field

†

symval

†

Value

BT.656, Y/C Mode,

or Raw Data Mode

TSI Mode

31–10

Reserved

–

0

Reserved. The reserved bit location is always read as 0. A

value written to this field has no effect.

9–1

PCRE

OF(value)

0–1FFh

Not used.

Contains the extension portion of the

program clock reference.

0

PCRM

OF(value)

0–1

Not used.

Contains the MSB of the program clock

reference.

† For CSL implementation, use the notation VP_TSISTCLKM_field_symval