Texas Instruments TMS320C64x DSP User Manual

Page 151

Video Display Mode Selection

Video Display Port

4-6

SPRU629

The image line counter (ILCOUNT) and the image pixel counter (IPCOUNT)

track the visible image within the field. ILCOUNT begins counting at the first

display image line in each field. IPCOUNT begins counting at the first dis-

played image pixel on each line. They stop counting when they reach the

image height and image width as specified in the video display field n image

size register (VDIMGSZn).

The video clock counter (VCCOUNT) counts VCLKIN transitions to determine

when to increment FPCOUNT and IPCOUNT as determined by the video

display mode. In Y/C mode, FPCOUNT and IPCOUNT increment on each

VCLKIN rising edge. In BT.656 mode, FPCOUNT and IPCOUNT increment on

every other VCLKIN rising edge. In raw mode, FPCOUNT and IPCOUNT

increment on every 1 to 16 VCLKIN cycles as programmed by the INCPIX bits

in the video display threshold register (VDTHRLD).

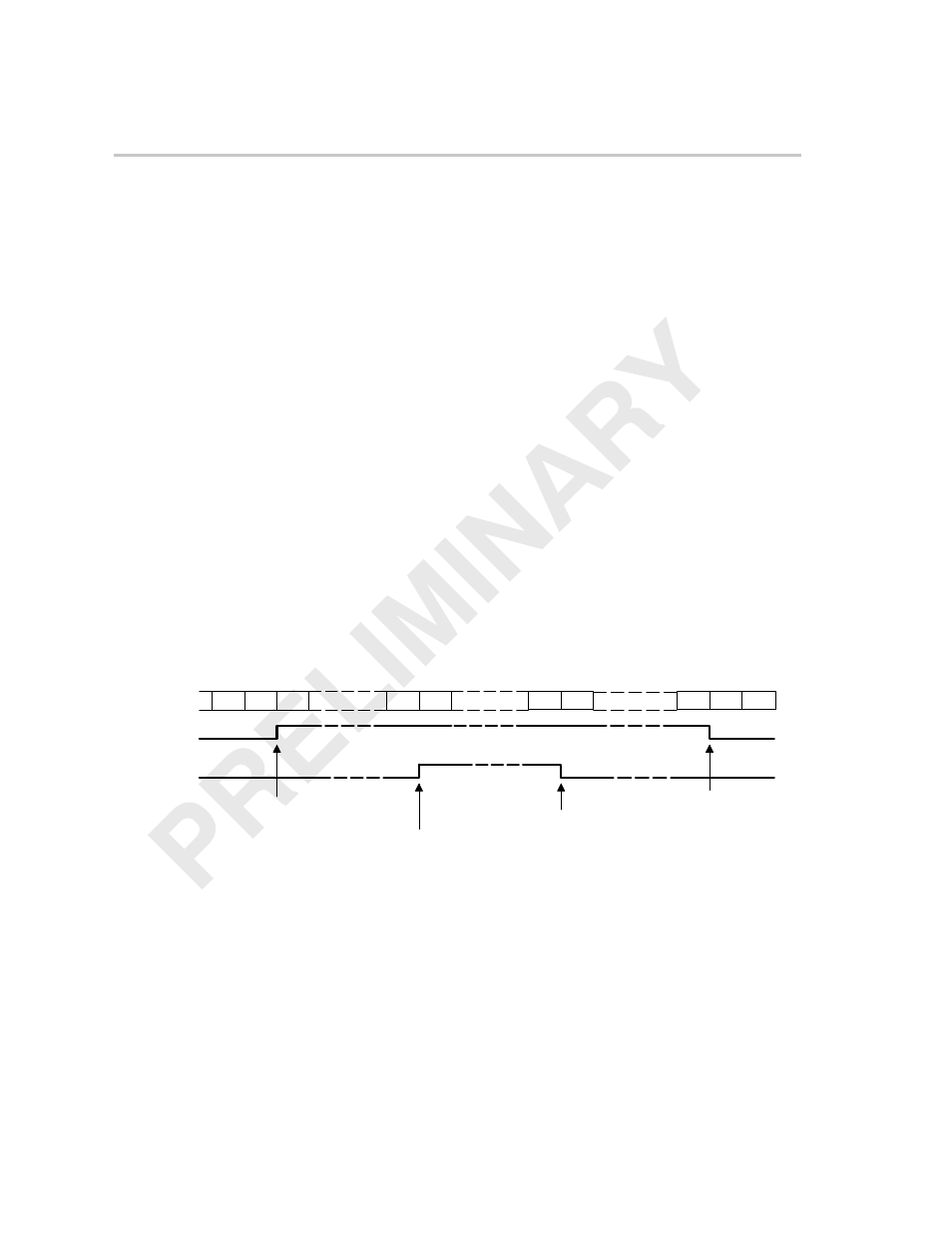

FPCOUNT and FLCOUNT are compared to various values to determine when

to assert and negate various control signals. The 12-bit FPCOUNT is used to

determine where to enable and disable horizontal sync and blanking informa-

tion along each scan line. The state of FPCOUNT is reflected in the VDXPOS

bits of the video display status register (VDSTAT). Figure 4–5 shows how the

horizontal blanking and horizontal synchronization signals are triggered.

(HBLNK and HSYNC are shown active high).

Figure 4–5. Horizontal Blanking and Horizontal Sync Timing

718

FPCOUNT

HBLNK

HSYNC

719 720

735 736

799 800

857

0

1

FPCOUNT = HBLNKSTART

FPCOUNT = HBLNKSTOP

FPCOUNT = HSYNCSTOP

FPCOUNT = HSYNCSTART

The 12-bit FLCOUNT counts which scan line is being generated. The

FLCOUNT is reset to 1 after reaching the count specified in VDFRMSZ. (For

BT.656 operation, the FRMHIGHT would be set to 525 (525/60 operation) or

625 (625/50 operation).) The state of FLCOUNT is reflected in the VDYPOS

bits of VDSTAT. Figure 4–6 shows how the vertical blanking, vertical synchro-

nization, and field identification signals are triggered. (VBLNK and VSYNC are

shown active high.)