Texas Instruments TMS320C64x DSP User Manual

Page 189

Display T

iming

Examples

4-44

V

ideo Display Port

SPRU629

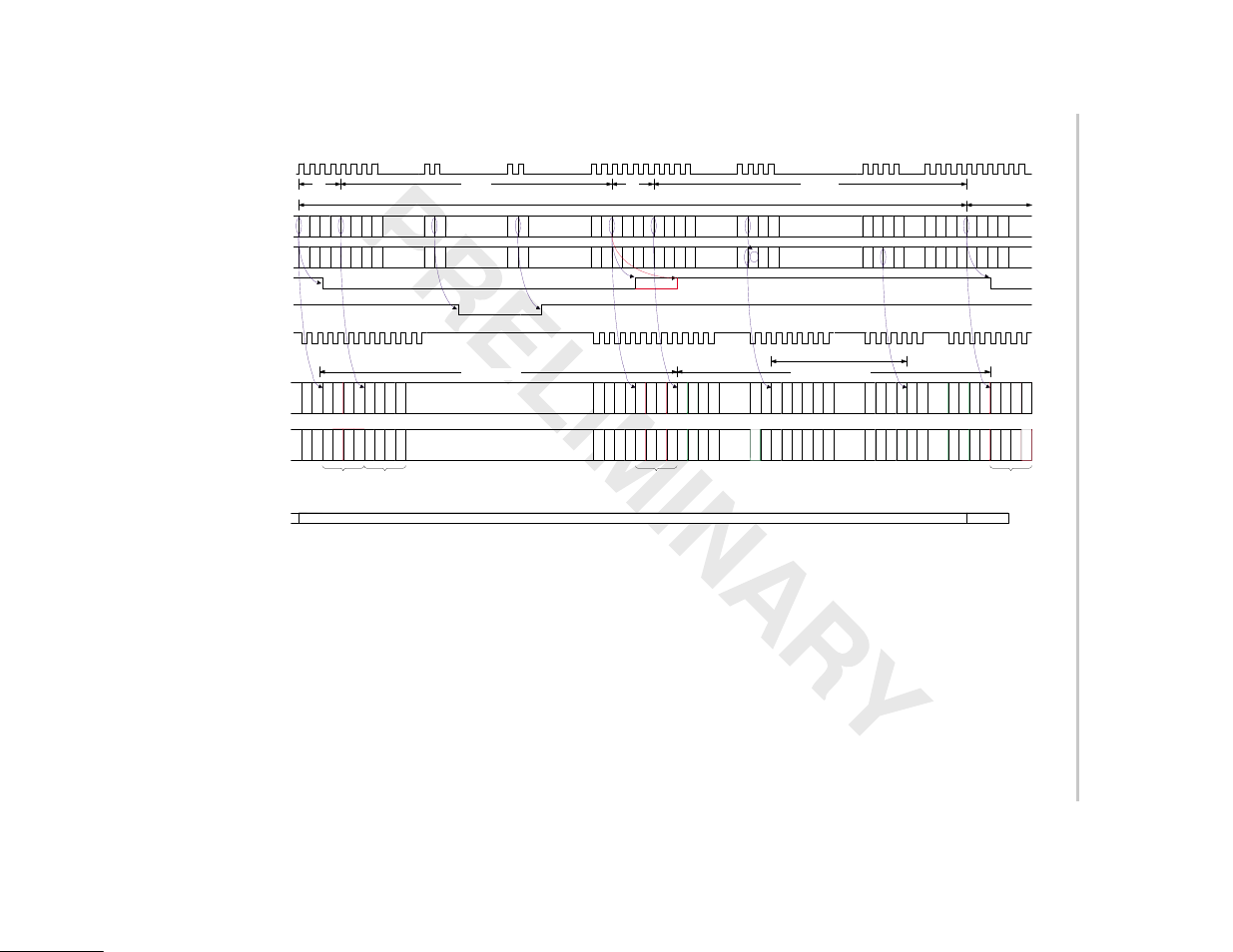

Figure 4–37. Y/C Progressive Display Horizontal Timing Example

‡

ЙЙ

ЙЙ

ЙЙ

VCLKIN

FPCOUNT

IPCOUNT

VCTL1 (HBLNK)† §

VCTL1 (HSYNC)† §

VCLKOUT

VDOUT[9–0] §

VDOUT[19–0] §

FLCOUNT

n – 1

n + 1

n

EAV

Blanking Data

SAV

EAV

Blanking

Active Video

Display Image

4

362

4

1280

One Line

Next Line

1280

1281

1282

1283

1284

1285

1286

1287

1263

1263

1263

1263

1263

1263

1263

1263

1263

1263

12631263

1263

12631263

1263

1263

1263

1263

1263

1263

1263

1263

1263

1263

1262

1263

1263

1263

1263

1263

1263

1263

1263

1263

1263

1263

1349

1350

1429

1430

1644

1645

1646

1647

1648

1649

0

1

2

33

7

8

9

10

1

0

2

1270

1271

1272

1273

1276

1277

1278

1279

1280

1281

1282

1283

Def

Y

Def

Y

FF

.C

00.

0

XY

.0

80.

0

80.

0

80.

0

80.

0

Def

Cb

Def

Cr

FF

.C

00.

0

00.

0

XY

.0

10.

0

10.

0

10.

0

10.

0

80.

0

10.

0

80.

0

80.

0

80.

0

10.

0

10.

0

10.

0

FF

.C

00.

0

00.

0

XY

.0

FF

.C

00.

0

00.

0

XY

.0

Def

Cb

Def

Cr

Def

Cb

Def

Cr

Def

Y

Def

Y

Def

Y

Def

Y

Def

Cr

Def

Cb

Def

Y

Def

Y

Cb0

Cr

0

Y0

Y1

Y2

Y3

Y4

Y5

Cb1

Cr

1

Cb2

Cr

2

Y1260

Y1261

Y1262

Y1263

Def

Y

Def

Y

Def

Y

Def

Y

Def

Y

Def

Y

FF

.C

00.

0

00.

0

XY

.0

FF

.C

00.

0

00.

0

XY

.0

Cb630

Cr630

Cb631

Cr631

Def

Cb

Def

Cr

Def

Cb

Def

Cr

Def

Cb

Def

Cr

00.

0

FRMWIDTH = 1650

IMGHOFF1 = 8

HSYNCSTART = 1350

HBLNKSTART = 1280

IMGHSIZE1 = 1264

HSYNCSTOP = 1430

HBLNKSTOP = 1646

IMGHOFF2 = n/a

IMGHSIZE2 = n/a

† Assumes VCT1P bit in VPCTL is set to 1 (active-low output). HSYNC output when VCTL1S bit in VDCTL is set to 00,

HBLNK output when VCTL1S bit is set 01.

‡ HBLNK operation when HBDLA bit in VDHBLNK is set to 1.

§ Diagram assumes a two VCLK pipeline delay between internal counters and output signals.