Figure 4–32. display line boundary example – Texas Instruments TMS320C64x DSP User Manual

Page 179

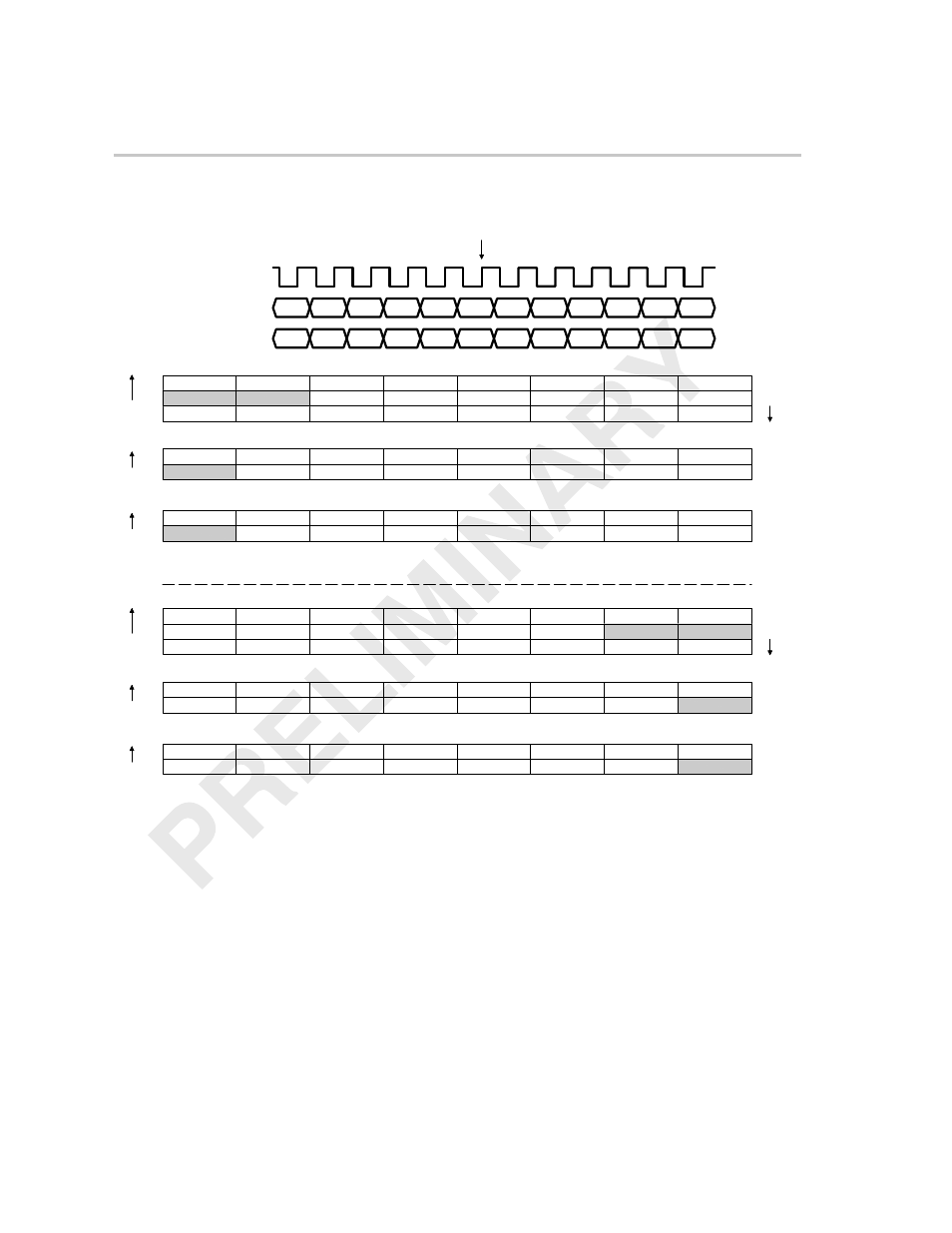

Display Line Boundary Conditions

Video Display Port

4-34

SPRU629

Figure 4–32. Display Line Boundary Example

Y FIFO

Cb FIFO

Y 74

Y 76

Y 78

Y73

Y 75

Y 77

Y 79

VDOUT[9–2]

VCLKOUT

63

5655

4847

4039

32

Y 5

Y 4

Y 7

Y 6

Y 69

Y 68

Y 71

Y 70

Y 77

Y 76

Cb 37

Cb 36

Cb 38

Little-Endian Packing

Y 80

Y 82

Y 81

Y 83

Cb 36

Cb 37

Cb 38

Cb 39

Cr 36

Cr 37

Cr 38

Cr 39

VDOUT[19–12]

Cb 40

Cb 41

Cr 40

Cr 41

Y 72

31

2423

1615

8 7

0

Y 1

Y 0

Y 3

Y 2

Y 65

Y 64

Y 67

Y 66

Y 73

Y 72

Y 75

Y 74

31

2423

1615

8 7

0

Cb 33

Cb 32

Cb 35

Cb 34

63

5655

4847

4039

32

IPCOUNT = IMGSIZE(78)

Cb 5

Cb 4

Cb 7

Cb 6

Cb 1

Cb 0

Cb 3

Cb 2

Cr FIFO

Cr 37

Cr 36

Cr 38

31

2423

1615

8 7

0

Cr 33

Cr 32

Cr 35

Cr 34

63

5655

4847

4039

32

Cr 5

Cr 4

Cr 7

Cr 6

Cr 1

Cr 0

Cr 3

Cr 2

Y FIFO

Cb FIFO

63

5655

4847

4039

32

Y 5

Y 4

Y 7

Y 6

Y 69

Y 68

Y 71

Y 70

Y 77

Y 76

Cb 37

Cb 36

Cb 38

Big-Endian Packing

31

2423

1615

8 7

0

Y 1

Y 0

Y 3

Y 2

Y 65

Y 64

Y 67

Y 66

Y 73

Y 72

Y 75

Y 74

31

2423

1615

8 7

0

Cb 33

Cb 32

Cb 35

Cb 34

63

5655

4847

4039

32

Cb 5

Cb 4

Cb 7

Cb 6

Cb 1

Cb 0

Cb 3

Cb 2

Cr FIFO

31

2423

1615

8 7

0

63

5655

4847

4039

32

Cr 37

Cr 36

Cr 38

Cr 33

Cr 32

Cr 35

Cr 34

Cr 5

Cr 4

Cr 7

Cr 6

Cr 1

Cr 0

Cr 3

Cr 2

Line n

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1