Texas Instruments TMS320C64x DSP User Manual

Page 14

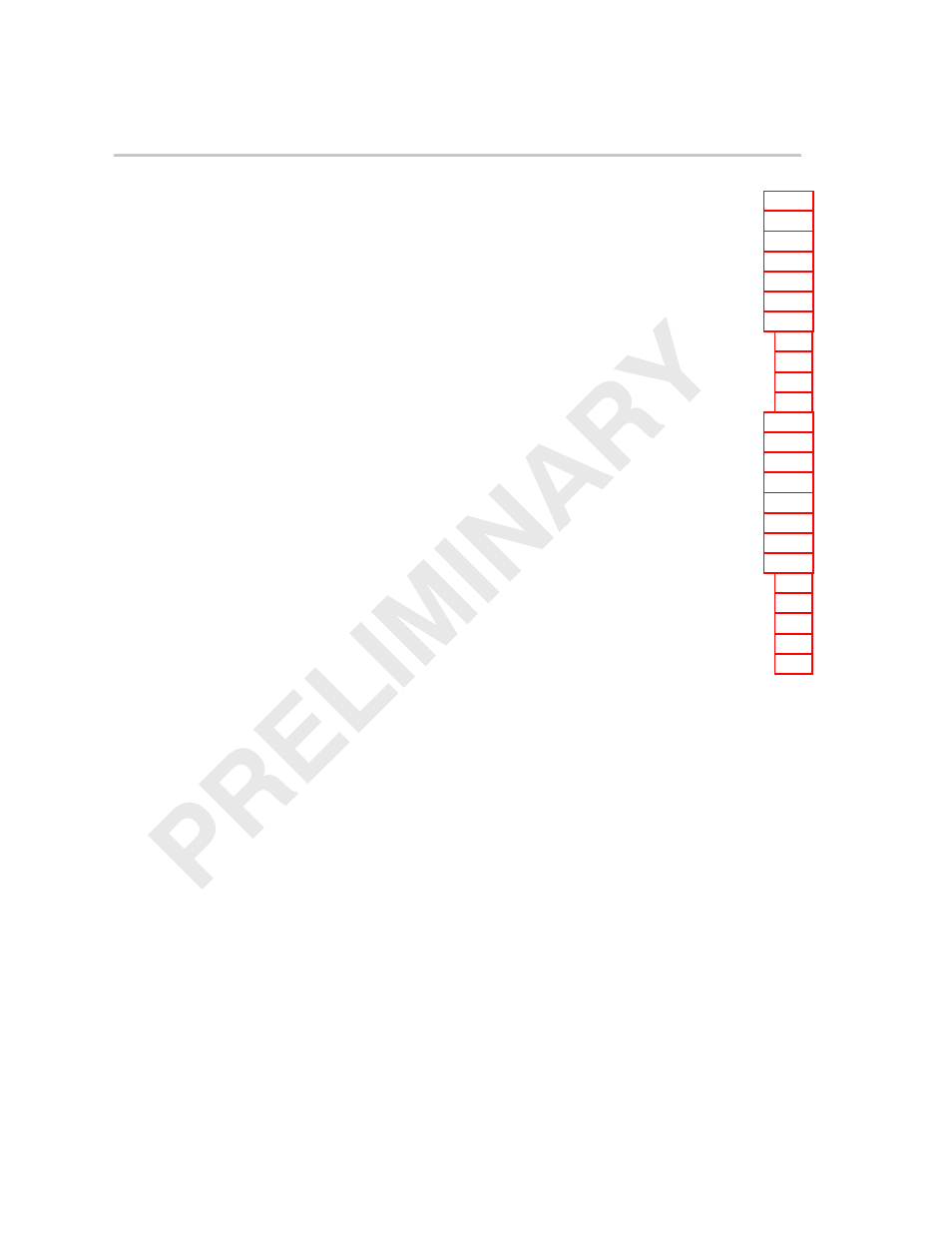

Figures

xiv

SPRU629

4–61

Video Display Clipping Register (VDCLIP)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–62

Video Display Default Display Value Register (VDDEFVAL)

. . . . . . . . . . . . . . . . . . . . . . . .

4–63

Video Display Default Display Value Register (VDDEFVAL)—Raw Data Mode

4–64

Video Display Vertical Interrupt Register (VDVINT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–65

Video Display Field Bit Register (VDFBIT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–66

Video Display Field 1 Vertical Blanking Bit Register (VDVBIT1)

. . . . . . . . . . . . . . . . . . . . .

4–67

Video Display Field 2 Vertical Blanking Bit Register (VDVBIT2)

. . . . . . . . . . . . . . . . . . . . .

5–1

Video Port Peripheral Identification Register (VPPID)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2

Video Port Peripheral Control Register (PCR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3

Video Port Pin Function Register (PFUNC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4

Video Port Pin Direction Register (PDIR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5

Video Port Pin Data Input Register (PDIN)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6

Video Port Pin Data Output Register (PDOUT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7

Video Port Pin Data Set Register (PDSET)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8

Video Port Pin Data Clear Register (PDCLR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9

Video Port Pin Interrupt Enable Register (PIEN)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10

Video Port Pin Interrupt Polarity Register (PIPOL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11

Video Port Pin Interrupt Status Register (PISTAT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12

Video Port Pin Interrupt Clear Register (PICLR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1

TSI System Block Diagram

6–2

Program Clock Reference (PCR) Header Format

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3

VIC Control Register (VICCTL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4

VIC Input Register (VICIN)

6–5

VIC Clock Divider Register (VICDIV)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .