Texas Instruments TMS320C64x DSP User Manual

Page 222

Video Display Registers

4-77

Video Display Port

SPRU629

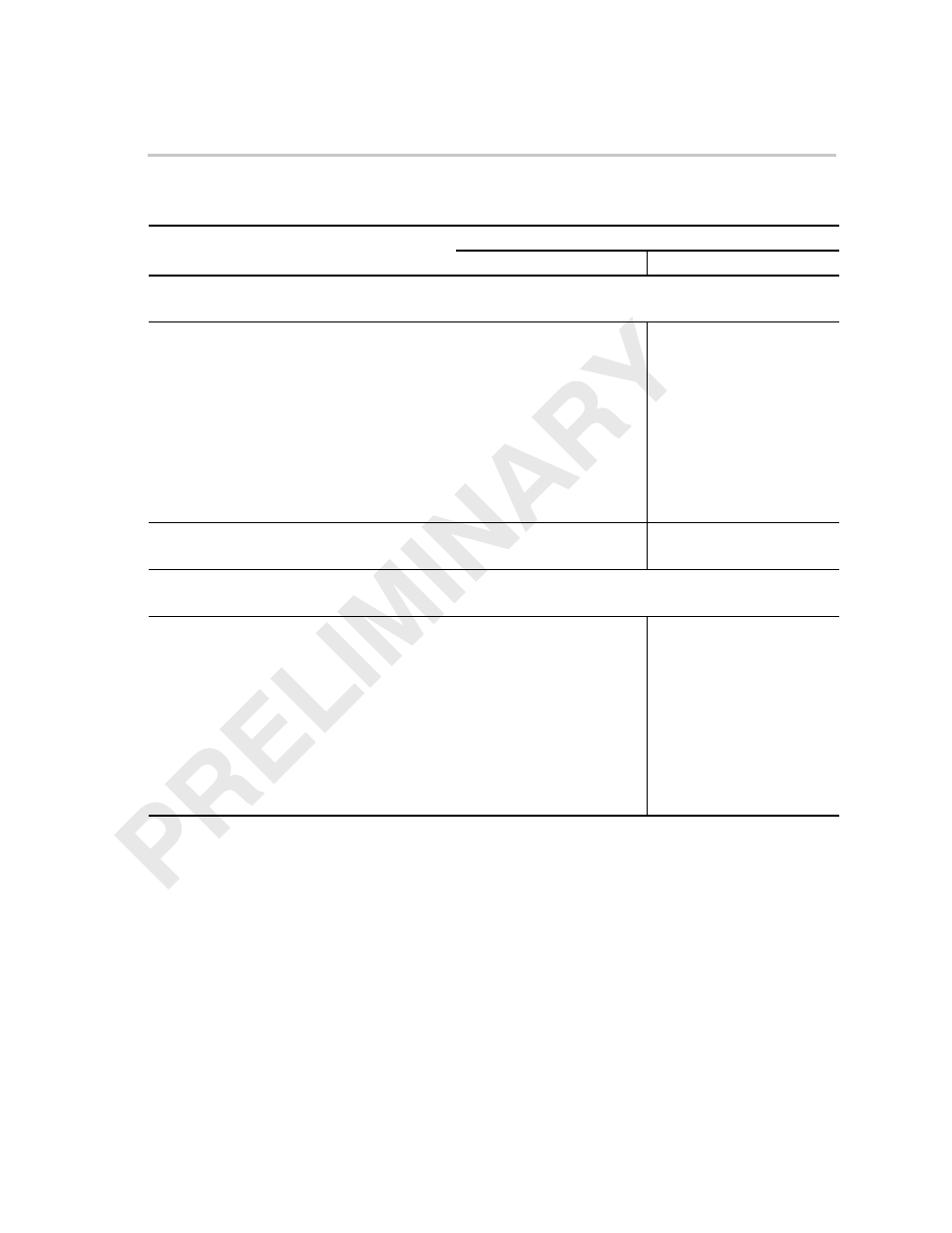

Table 4–20. Video Display Threshold Register (VDTHRLD) Field Descriptions

Description

Bit

field

†

symval

†

Value

BT.656 and Y/C Mode

Raw Data Mode

31–26

Reserved

–

0

Reserved. The reserved bit location is always read as 0. A

value written to this field has no effect.

25–16

VDTHRLD2

OF(value)

0–3FFh

Field 2 threshold. Whenever

there are at least VDTHRLD

doublewords of space in the

Y display FIFO, a new Y

DMA event may be

generated. Whenever there

are at least

½

VDTHRLD

doublewords of space in the

Cb or Cr display FIFO, a

new Cb or Cr DMA event

may be generated.

Field 2 threshold. Whenever

there are at least VDTHRLD

doublewords of space in the

display FIFO, a new Y DMA

event may be generated.

15–12

INCPIX

OF(value)

0–Fh

Not used.

FPCOUNT is incremented

every INCPIX output clocks.

11–10

Reserved

–

0

Reserved. The reserved bit location is always read as 0. A

value written to this field has no effect.

9–0

VDTHRLD1

OF(value)

0–3FFh

Field 1 threshold. Whenever

there are at least VDTHRLD

doublewords of space in the

Y display FIFO, a new Y

DMA event may be

generated. Whenever there

are at least

½

VDTHRLD

doublewords of space in the

Cb or Cr display FIFO, a

new Cb or Cr DMA event

may be generated.

Field 1 threshold. Whenever

there are at least VDTHRLD

doublewords of space in the

display FIFO, a new Y DMA

event may be generated.

† For CSL implementation, use the notation VP_VDTHRLD_field_symval