Texas Instruments TMS320C64x DSP User Manual

Page 105

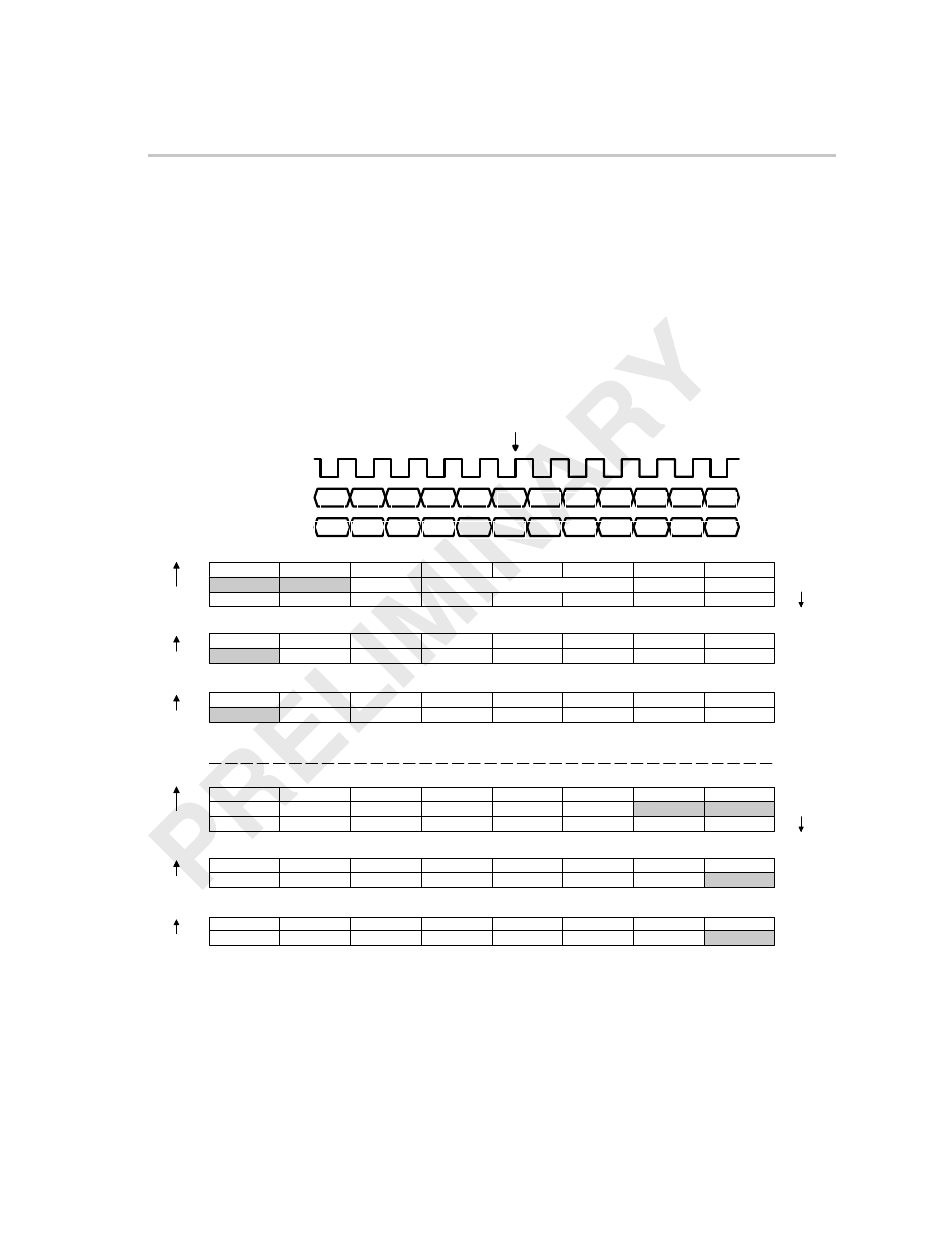

Capture Line Boundary Conditions

3-43

Video Capture Port

SPRU629

In Figure 3–28 (8-bit Y/C mode), the line length is not a doubleword. When the

condition HCOUNT = VCXSTOP occurs, the FIFO location is written even

though 8 bytes have not been received. The next capture line then begins in

the next FIFO location at byte 0. This operation extends to all capture modes.

In the case of TSI and raw data modes, there are no lines. In these modes, a

final write at the end of the packet must be performed when the packet data

count equals the 24-bit combined value of VCXCOUNT and VCYCOUNT.

Figure 3–28. Capture Line Boundary Example

Y FIFO

Cb FIFO

Y 74

Y 76

YDEF

Y73

Y 75

Y 77

YDEF

VDOUT[9–2]

VCLKOUT

63

56 55

48 47

40 39

32

Y 5

Y 4

Y 7

Y 6

Y 69

Y 68

Y 71

Y 70

Y 77

Y 76

Cb 37

Cb 36

Cb 38

Little-Endian Packing

YDEF

YDEF

YDEF

YDEF

Cb 36

Cb 37

Cb 38

CbDEF

Cr 36

Cr 37

Cr 38

CrDEF

VDOUT[19–12]

CbDEF

CbDEF

CrDEF

CrDEF

Y 72

31

24 23

16 15

8 7

0

Y 1

Y 0

Y 3

Y 2

Y 65

Y 64

Y 67

Y 66

Y 73

Y 72

Y 75

Y 74

31

24 23

16 15

8 7

0

Cb 33

Cb 32

Cb 35

Cb 34

63

56 55

48 47

40 39

32

IPCOUNT = IMGHSIZE(78)

Cb 5

Cb 4

Cb 7

Cb 6

Cb 1

Cb 0

Cb 3

Cb 2

Cr FIFO

Cr 37

Cr 36

Cr 38

31

24 23

16 15

8 7

0

Cr 33

Cr 32

Cr 35

Cr 34

63

56 55

48 47

40 39

32

Cr 5

Cr 4

Cr 7

Cr 6

Cr 1

Cr 0

Cr 3

Cr 2

Y FIFO

Cb FIFO

63

56 55

48 47

40 39

32

Y 5

Y 4

Y 7

Y 6

Y 69

Y 68

Y 71

Y 70

Y 77

Y 76

Cb 37

Cb 36

Cb 38

Big-Endian Packing

31

24 23

16 15

8 7

0

Y 1

Y 0

Y 3

Y 2

Y 65

Y 64

Y 67

Y 66

Y 73

Y 72

Y 75

Y 74

31

24 23

16 15

8 7

0

Cb 33

Cb 32

Cb 35

Cb 34

63

56 55

48 47

40 39

32

Cb 5

Cb 4

Cb 7

Cb 6

Cb 1

Cb 0

Cb 3

Cb 2

Cr FIFO

31

24 23

16 15

8 7

0

63

56 55

48 47

40 39

32

Cr 37

Cr 36

Cr 38

Cr 33

Cr 32

Cr 35

Cr 34

Cr 5

Cr 4

Cr 7

Cr 6

Cr 1

Cr 0

Cr 3

Cr 2

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1

Line n

Line n+1