Texas Instruments TMS320C64x DSP User Manual

Page 204

Video Display Registers

4-59

Video Display Port

SPRU629

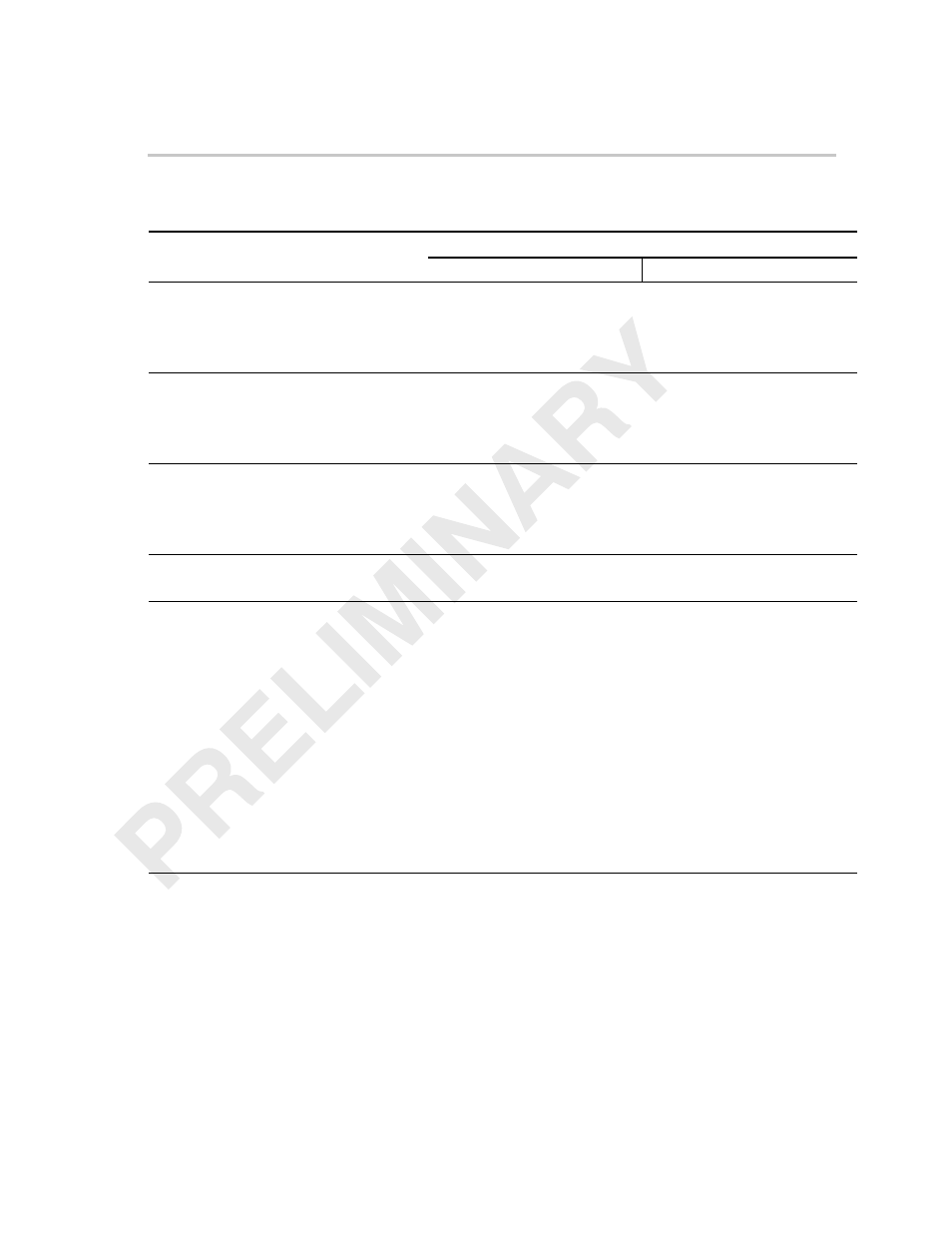

Table 4–7. Video Display Control Register (VDCTL) Field Descriptions (Continued)

Bit

Description

Value

symval

†

field

†

Bit

Raw Data Mode

BT.656 and Y/C Mode

Value

symval

†

field

†

6

FRAME

‡

Display frame bit.

NONE

0

Do not display frame.

FRMDIS

1

Display frame.

5

DF2

‡

Display field 2 bit.

NONE

0

Do not display field 2.

FLDDIS

1

Display field 2.

4

DF1

‡

Display field 1 bit.

NONE

0

Do not display field 1.

FLDDIS

1

Display field 1.

3

Reserved

–

0

Reserved. The reserved bit location is always read as 0. A value

written to this field has no effect.

2–0

DMODE

Display mode select bit.

BT656B

0

Enables 8-bit BT.656 mode.

BT656D

1h

Enables 10-bit BT.656 mode.

RAWB

2h

Enables 8-bit raw data mode.

RAWD

3h

Enables 10-bit raw data mode.

YC16

4h

Enables 8-bit Y/C mode.

YC20

5h

Enables 10-bit Y/C mode.

RAW16

6h

Enables 16-bit raw data mode.

RAW20

7h

Enables 20-bit raw data mode.

† For CSL implementation, use the notation VP_VDCTL_field_symval

‡ For complete encoding of these bits, see Table 4–4.