2 switch fabric csr reads, Switch fabric csr reads, Figure 6.1 – SMSC LAN9311i User Manual

Page 57: Datasheet 6.2.2 switch fabric csr reads, Csr write, Csr write auto increment / decrement, Csr write direct address

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

57

Revision 1.4 (08-19-08)

DATASHEET

6.2.2

Switch Fabric CSR Reads

To perform a read of an individual switch fabric register, the read cycle must be initiated by performing

a single write to the

Switch Fabric CSR Interface Command Register (SWITCH_CSR_CMD)

CSR_BUSY (bit 31) set, the CSR_ADDRESS field (bits 15:0) set to the desired register address, the

R_nW (bit 30) set, and the AUTO_INC and AUTO_DEC fields cleared. Valid data is available for

reading when the CSR_BUSY bit is cleared, indicating that the data can be read from the

CSR Interface Data Register (SWITCH_CSR_DATA)

A second read method may be used which utilizes the auto increment/decrement function of the

Fabric CSR Interface Command Register (SWITCH_CSR_CMD)

for reading sequential register

addresses. When using this method, the

Switch Fabric CSR Interface Command Register

must first be written with the auto increment(AUTO_INC) or auto

decrement(AUTO_DEC) bit set, the CSR_ADDRESS field written with the desired register address,

and the R_nW bit set. The completion of a read cycle is indicated by the clearing of the CSR_BUSY

bit, at which time the data can be read from the

Switch Fabric CSR Interface Data Register

. When the data is read, the address in the

Command Register (SWITCH_CSR_CMD)

is incremented or decremented accordingly, and another

read cycle is started automatically. The user should clear the AUTO_INC and AUTO_DEC bits before

reading the last data to avoid an unintended read cycle.

illustrates the process required to perform a switch fabric CSR read. The minimum wait

periods as specified in

Table 8.1, “Read After Write Timing Rules,” on page 103

are required where

noted.

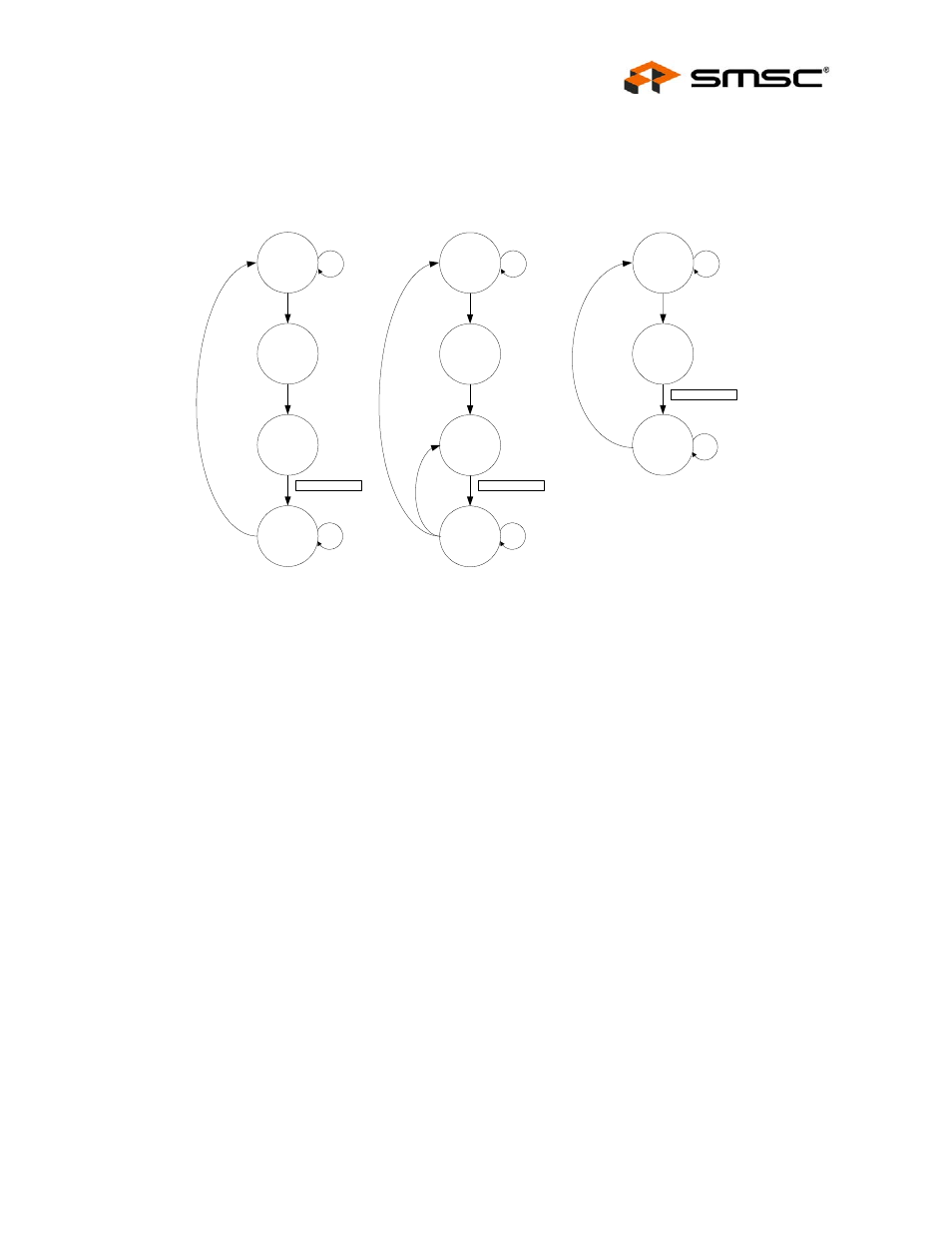

Figure 6.1 Switch Fabric CSR Write Access Flow Diagram

Idle

Write Data

Register

Write

Command

Register

Read

Command

Register

CSR_BUSY = 0

CSR Write

CSR_BUSY = 1

Idle

Write Data

Register

Write

Command

Register

Read

Command

Register

CSR_BUSY = 0

CSR Write Auto

Increment /

Decrement

CSR_BUSY = 1

Idle

Write

Direct

Data

Register

Range

Read

Command

Register

CSR_BUSY = 0

CSR Write Direct

Address

CSR_BUSY = 1

min wait period

min wait period

min wait period